## **Hybrid Programming in HPC – MPI+X**

Claudia Blaas-Schenner<sup>1)</sup>

Georg Hager<sup>2)</sup>

Rolf Rabenseifner<sup>3)</sup>

rabenseifner@hlrs.de

- 1) VSC Research Center, TU Wien, Vienna, Austria (hands-on labs)

- <sup>2)</sup> Erlangen National High Performance Computing Center (NHR@FAU), FAU, Germany

- <sup>3)</sup> High Performance Computing Center (HLRS), University of Stuttgart, Germany

PTC ONLINE COURSE @ VSC Vienna, Dec 12-14, 2022

http://tiny.cc/MPIX-VSC

## Warmup survey

- For quizzes and surveys,

- Keep a browser tab open on <a href="https://menti.com">https://menti.com</a>

- To join the quizzes and surveys,

enter the number given in the menti.com screen share on the top of the screen

- Alternatively, click on the link in the Zoom chat

- Have fun ;-)

#### **General outline**

#### Introduction

#### **Programming Models** (13)

- MPI + OpenMP on multi/many-core (14) + Exercises

- MPI + Accelerators (99)

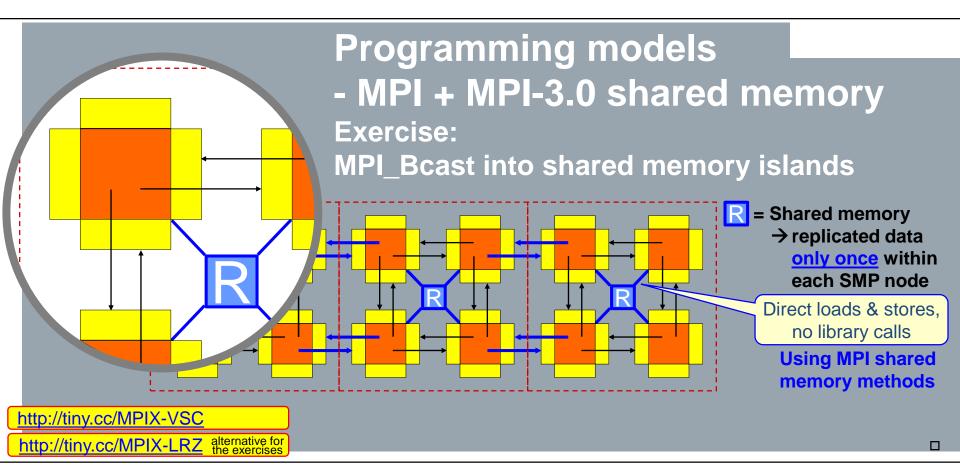

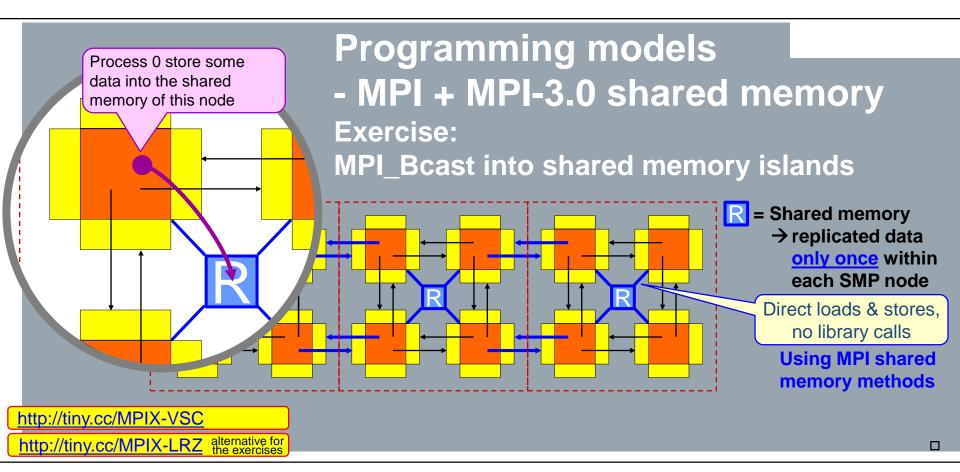

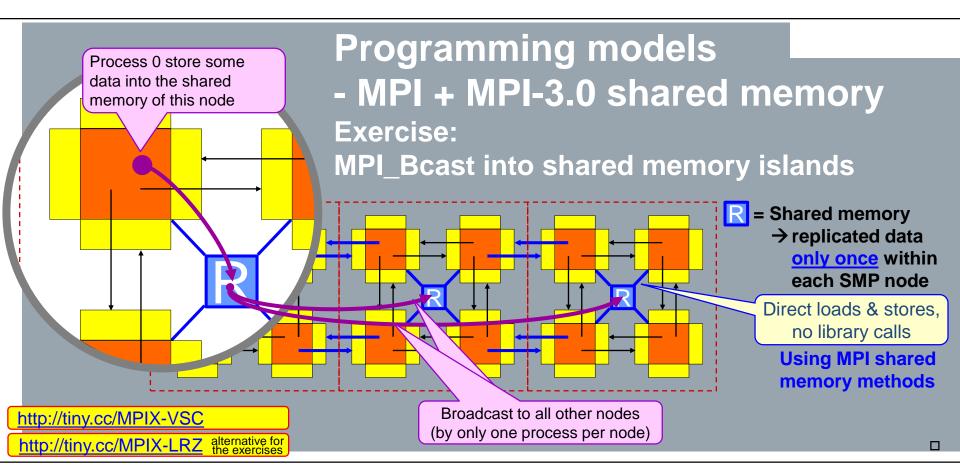

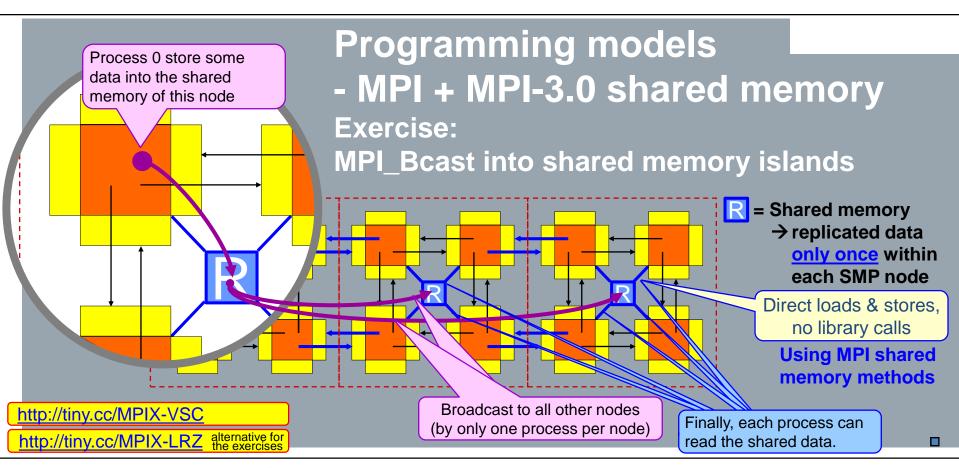

- MPI + MPI-3 shared memory (115) + Exercise (143)

- Pure MPI communication (175)

Conclusions (Summary (232), Acknowledgements (238), Conclusions (239)

Appendix (240) (Abstract (240), Authors (240), Solutions (245)

## Introduction

Hardware and programming models

Hardware Bottlenecks

Questions addressed in this tutorial

Remarks on Cost-Benefit Calculation

## Hardware and programming models

- MPI + threading

- OpenMP

- Cilk(+)

- TBB (Threading Building Blocks)

- MPI + MPI shared memory

- MPI + accelerator

- OpenACC

- OpenMP accelerator support

- CUDA

- OpenCL, Kokkos, SYCL,...

- Pure MPI communication

Which programming model is fastest?

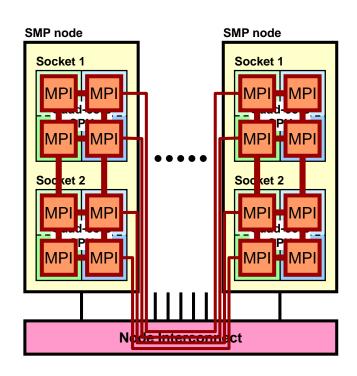

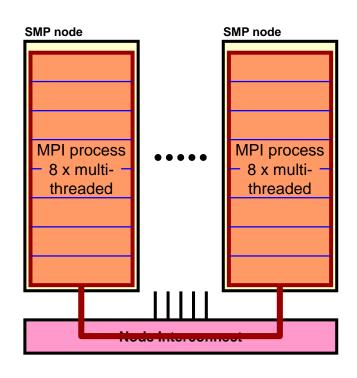

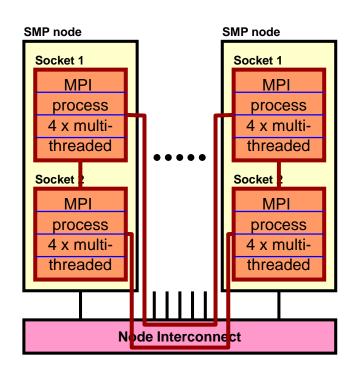

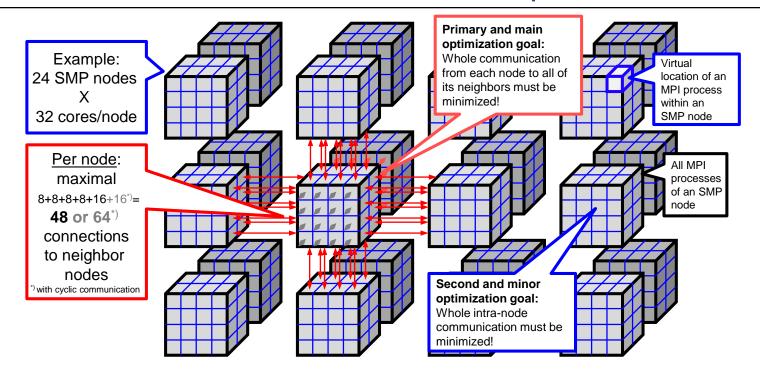

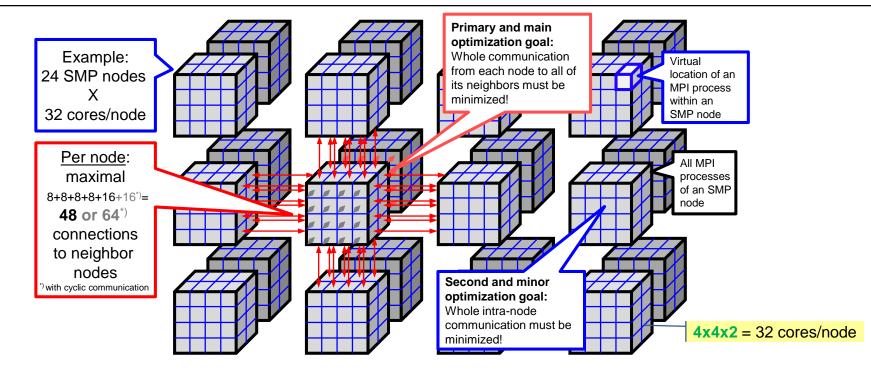

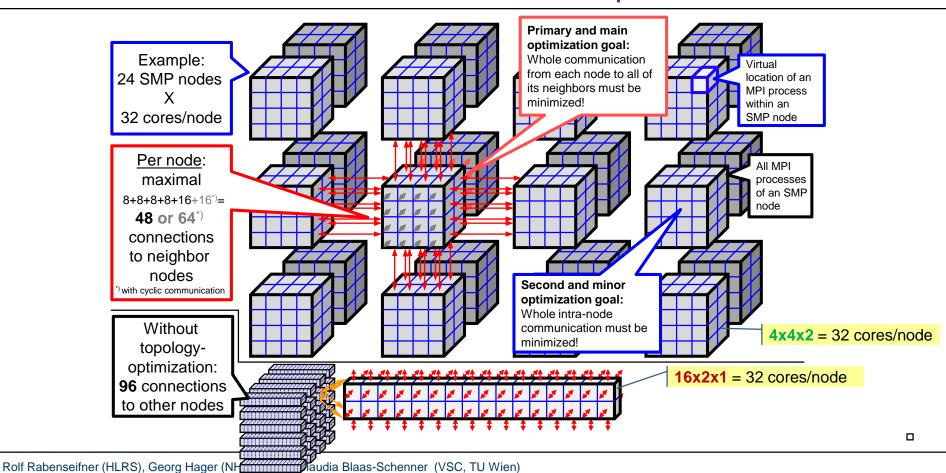

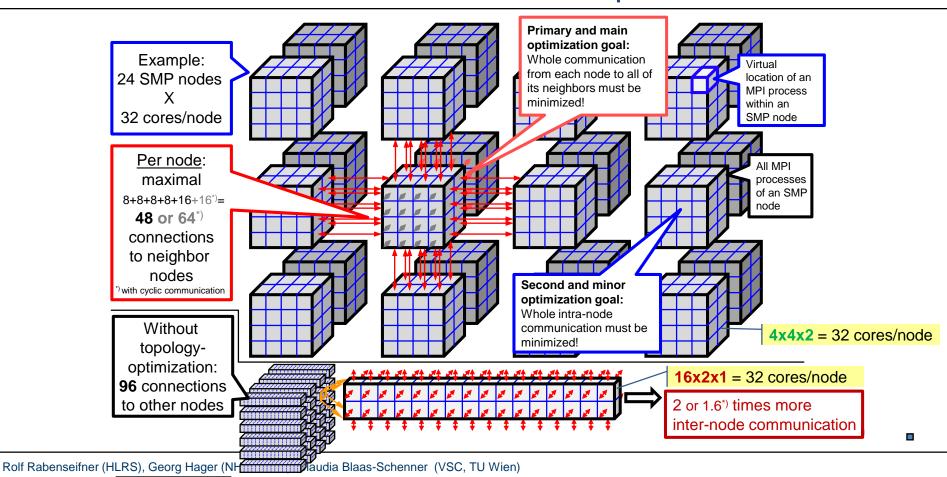

- Which programming model is fastest?

- MPI everywhere?

- Which programming model is fastest?

- MPI everywhere?

- Fully hybrid MPI & OpenMP?

- Which programming model is fastest?

- MPI everywhere?

- Which programming model is fastest?

- MPI everywhere?

Fully hybrid MPI & OpenMP?

Something between? (Mixed model)

Often hybrid programming slower than pure MPI

Examples, Reasons,

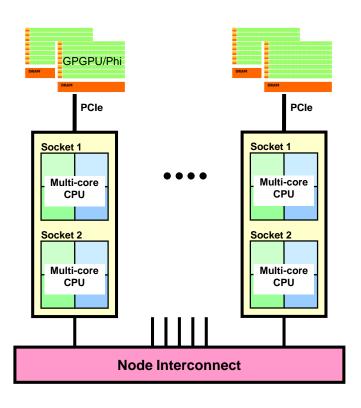

## More Options with accelerators

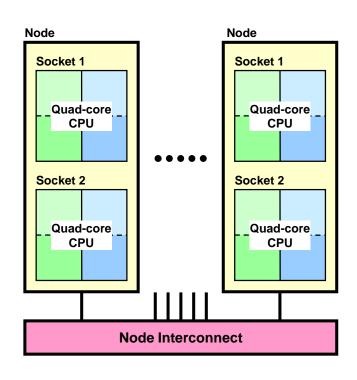

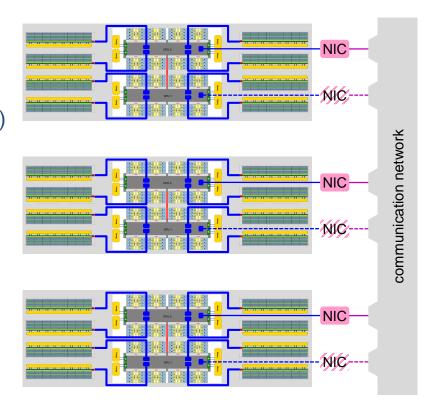

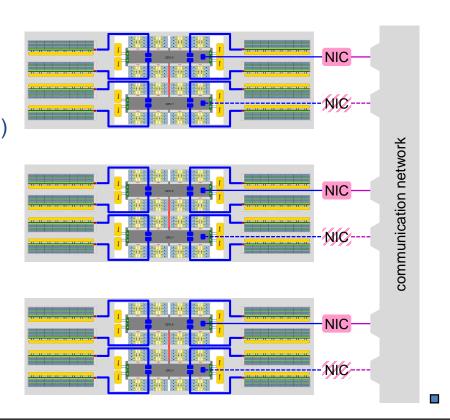

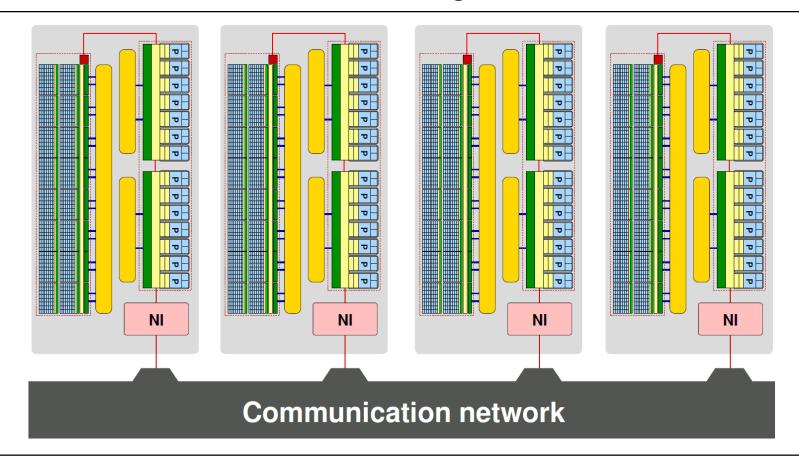

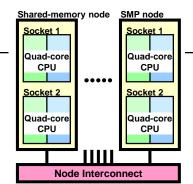

#### Hierarchical hardware

Many levels

#### Hierarchical parallel programming

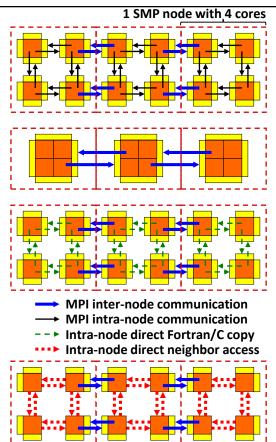

- Many options for MPI+X: one MPI process per

- node

- CPU

- ccNUMA domain

- [...]

- core

- hyper-thread

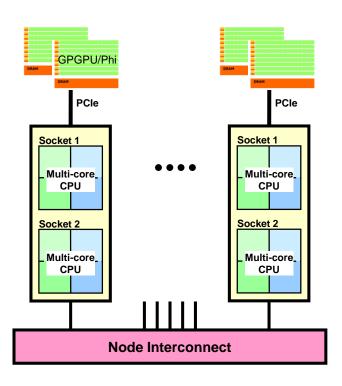

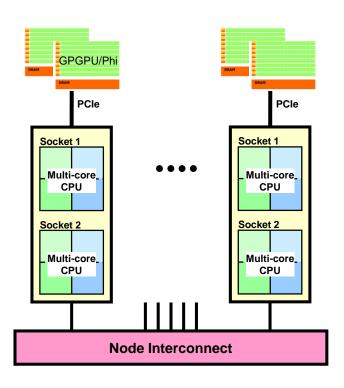

## More Options with accelerators

#### Hierarchical hardware

Many levels

#### Hierarchical parallel programming

- Many options for MPI+X: one MPI process per

- node

- CPU

- ccNUMA domain

- [...]

- core

- hyper-thread

bottleneck?

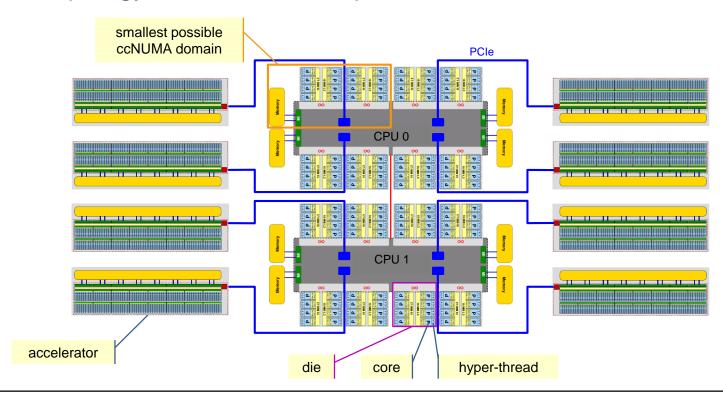

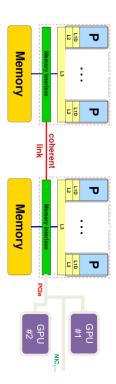

#### Dual-CPU ccNUMA + accelerator node architecture

#### Actual topology of a modern compute node

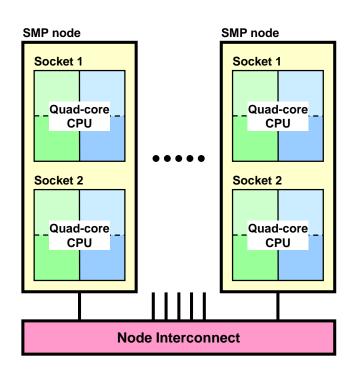

#### Hardware bottlenecks

- Multicore cluster

- Computation

- Memory bandwidth

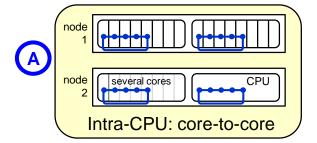

- Intra-CPU communication (i.e., core-to-core)

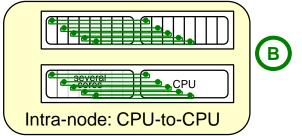

- Intra-node communication (i.e., CPU-to-CPU)

- Inter-node communication

#### Hardware bottlenecks

- Multicore cluster

- Computation

- Memory bandwidth

- Intra-CPU communication (i.e., core-to-core)

- Intra-node communication (i.e., CPU-to-CPU)

- Inter-node communication

- Cluster with CPU+Accelerators

- Within the accelerator

- Computation

- Memory bandwidth

- Core-to-Core communication

- Within the CPU and between the CPUs

- See above

- Link between CPU and accelerator

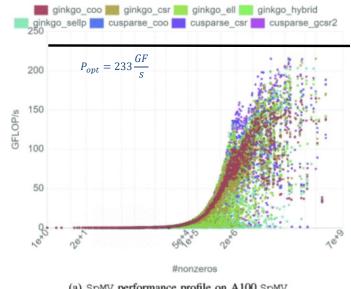

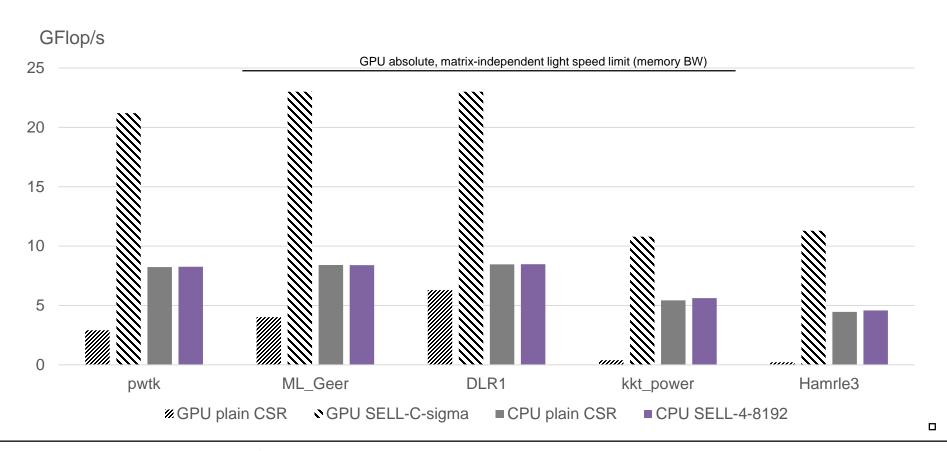

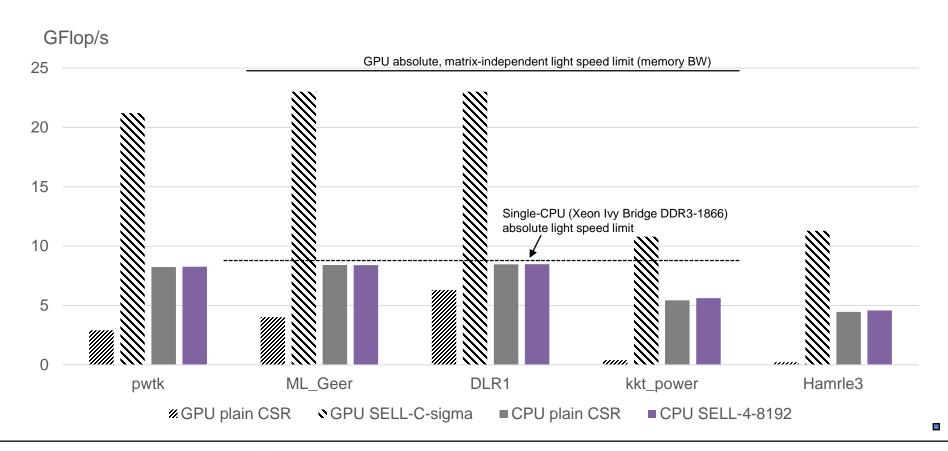

## Example: Hardware bottlenecks in SpMV

- Sparse matrix-vector-multiply with stored matrix entries

- Bottleneck: memory bandwidth of each CPU

SpMV with calculated matrix entries

(many complex operations per entry)

- Bottleneck: computational speed of each core

- SpMV with highly scattered matrix entries

- Bottleneck: Inter-node communication

## Example: Hardware bottlenecks in SpMV

- Sparse matrix-vector-multiply with stored matrix entries

- Bottleneck: memory bandwidth of each CPU

SpMV with calculated matrix entries

(many complex operations per entry)

- Bottleneck: computational speed of each core

- SpMV with highly scattered matrix entries

- Bottleneck: Inter-node communication

What is the performance impact of system topology?

- What is the performance impact of system topology?

- How do I map my programming model on the system to my advantage?

- How do I do the split into MPI+X?

- Where do my processes/threads run? How do I take control?

- Where is my data?

- How can I minimize communication overhead?

- What is the performance impact of system topology?

- How do I map my programming model on the system to my advantage?

- How do I do the split into MPI+X?

- Where do my processes/threads run? How do I take control?

- Where is my data?

- How can I minimize communication overhead?

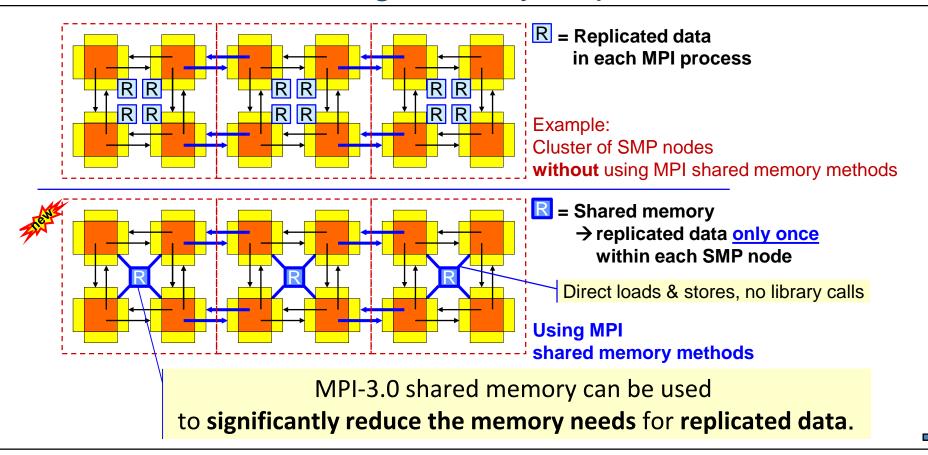

- How does hybrid programming help with typical HPC problems?

- Can it reduce communication overhead?

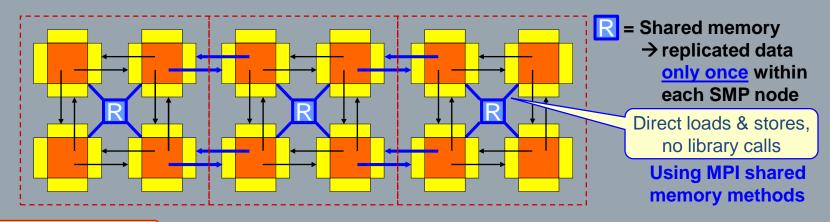

- Can it reduce replicated data?

- What is the performance impact of system topology?

- How do I map my programming model on the system to my advantage?

- How do I do the split into MPI+X?

- Where do my processes/threads run? How do I take control?

- Where is my data?

- How can I minimize communication overhead?

- How does hybrid programming help with typical HPC problems?

- Can it reduce communication overhead?

- Can it reduce replicated data?

- How can I leverage multiple accelerators?

- What are typical challenges?

#### Remarks on Cost-Benefit Calculation

#### Costs – for optimization effort

- e.g., additional OpenMP parallelization

- e.g., 3 person month x 5,000 € = -15,000 € (full costs)

#### Benefit – from reduced CPU utilization

- e.g., Example 1: 100,000 € hardware costs of the cluster

x 20% used by this application over whole lifetime of the cluster

x 7% performance win through the optimization

= +1,400 € → total loss = 13,600 €

- e.g., Example 2: **10 Mio € system** x 5% used x 8% performance win = +40,000 € → **total win = 25,000 €**

#### Question: Do you want to spend work hours without a final benefit?

## Programming models

- MPI + OpenMP on multi/many-core + Exercise

- MPI + MPI-3.0 shared memory + Exercise

- Pure MPI communication + Exercise

- MPI + Accelerators

# Programming models - MPI + OpenMP

| General considerations                         | slide <u>15</u> |

|------------------------------------------------|-----------------|

| How to compile, link, and run                  | <u>20</u>       |

| Hands-on: Hello hybrid!                        | <u>28</u>       |

| System topology, ccNUMA, and memory bandwid    | dth <u>30</u>   |

| Memory placement on ccNUMA systems             | <u>42</u>       |

| Topology and affinity on multicore             | <u>51</u>       |

| Hands-on: Pinning                              | <u>66</u>       |

| Case study: The Multi-Zone NAS Parallel Benchi | marks <u>67</u> |

| Hands-on: Masteronly hybrid Jacobi             | <u>74</u>       |

| Overlapping communication and computation      | <u>77</u>       |

| Communication overlap with OpenMP taskloops    | <u>84</u>       |

| Hands-on: Taskloop-based hybrid Jacobi         | <u>94</u>       |

| Main advantages, disadvantages, conclusions    | <u>95</u>       |

## Programming models

- MPI + OpenMP

#### **General considerations**

#### > General considerations

How to compile, link, and run

Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth

Memory placement on ccNUMA systems

Topology and affinity on multicore

Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

## Potential advantages of MPI+OpenMP

#### Simple level

- Leverage additional levels of parallelism

- Scaling to higher number of cores

- Adding OpenMP with incremental additional parallelization

- Enable flexible load balancing on OpenMP level

- Fewer MPI processes leave room for assigning workload more evenly

- MPI processes with higher workload could employ more threads

- Cheap OpenMP load balancing (tasking, dynamic/guided loops)

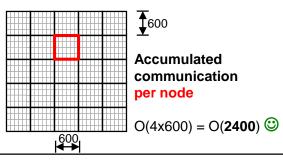

- Lower communication overhead (possibly)

- Few "fat" MPI processes vs many "skinny" processes

- Fewer messages and smaller amount of data communicated

- Lower memory requirements due to fewer MPI processes

- Reduced amount of application halos & replicated data

- Reduced size of MPI internal buffer space

#### Advanced level

Explicit communication/computation overlap

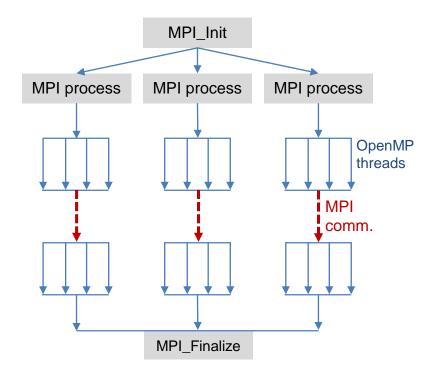

#### Special MPI init for multi-threaded MPI processes is required:

Main thread = thread that called MPI\_Init\_thread. Recommendation: Start MPI Init\_thread from OpenMP master thread → OpenMP master = MPI main thread

#### Special MPI init for multi-threaded MPI processes is required:

Possible values for thread\_level\_required (increasing order):

```

MPI_THREAD_SINGLE

MPI_THREAD_FUNNELED

MPI_THREAD_SERIALIZED

MPI_THREAD_MULTIPLE

MPI_THREAD_MULTIPLE

Only one thread will execute

Only main¹) thread will make MPI-calls

Multiple threads may make MPI-calls, but only one at a time

Multiple threads may call MPI, with no restrictions

```

Main thread = thread that called MPI\_Init\_thread.

Recommendation: Start MPI\_Init\_thread from OpenMP master thread → OpenMP master = MPI main thread

#### Special MPI init for multi-threaded MPI processes is required:

Possible values for thread\_level\_required (increasing order):

```

MPI_THREAD_SINGLE

Only one thread will execute

```

- MPI\_THREAD\_FUNNELED Only main<sup>1)</sup> thread will make MPI-calls

- MPI THREAD SERIALIZED Multiple threads may make MPI-calls, but only one at a time

- MPI THREAD MULTIPLE Multiple threads may call MPI, with no restrictions

may imply higher latencies due to some internal locks

<sup>1)</sup> Main thread = thread that called MPI\_Init\_thread. Recommendation: Start MPI Init\_thread from OpenMP master thread → OpenMP master = MPI main thread

#### Special MPI init for multi-threaded MPI processes is required:

• Possible values for thread level required (increasing order):

```

- MPI THREAD SINGLE Only one thread will execute

```

- MPI\_THREAD\_FUNNELED Only main<sup>1)</sup> thread will make MPI-calls

- MPI THREAD SERIALIZED Multiple threads may make MPI-calls, but only one at a time

- MPI THREAD MULTIPLE Multiple threads may call MPI, with no restrictions

- returned thread\_level\_provided may be less or more than thread\_level\_required

```

→ if (thread_level_provided < thread_level_required) MPI_Abort(...);</pre>

```

latencies due to some internal locks

may imply higher

Main thread = thread that called MPI\_Init\_thread.

Recommendation: Start MPI Init\_thread from OpenMP master thread → OpenMP master = MPI main thread

#### Special MPI init for multi-threaded MPI processes is required:

• Possible values for thread level required (increasing order):

```

- MPI THREAD SINGLE Only one thread will execute

```

- MPI\_THREAD\_FUNNELED Only main<sup>1)</sup> thread will make MPI-calls

- MPI THREAD SERIALIZED Multiple threads may make MPI-calls, but only one at a time

- MPI THREAD MULTIPLE Multiple threads may call MPI, with no restrictions

returned thread\_level\_provided may be less or more than thread\_level\_required

```

→ if (thread_level_provided < thread_level_required) MPI_Abort(...);</pre>

```

recommended directly after MPI Init thread

may imply higher latencies due to

some internal locks

Main thread = thread that called MPI\_Init\_thread.

Recommendation: Start MPI\_Init\_thread from OpenMP master thread → OpenMP master = MPI main thread

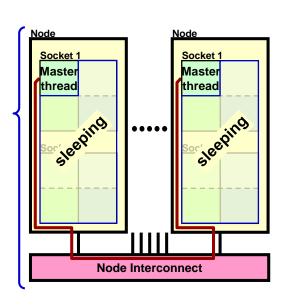

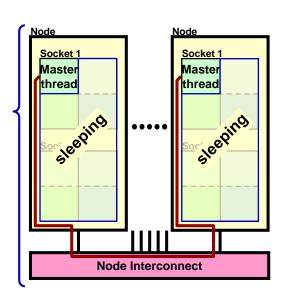

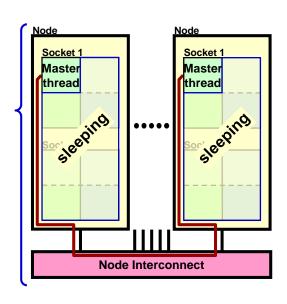

## Hybrid MPI+OpenMP masteronly style

```

for (iterations) {

#pragma omp parallel

numerical code

/*end omp parallel */

/* on master only */

MPI_Isend();

MPI_Irecv();

MPI_Waitall();

} /* end for loop */

```

masteronly style: MPI only outside of parallel regions

## Hybrid MPI+OpenMP masteronly style

```

for (iterations) {

#pragma omp parallel

numerical code

/*end omp parallel */

/* on master only */

MPI_Isend();

MPI_Irecv();

MPI_Waitall();

} /* end for loop */

```

#### Advantages

- Simplest possible hybrid model

- Thread-parallel execution and MPI communication strictly separate

- Minimally required MPI thread support level:

MPI\_THREAD\_FUNNELED

masteronly style: MPI only outside of parallel regions

## Hybrid MPI+OpenMP masteronly style

```

for (iterations) {

#pragma omp parallel

numerical code

/*end omp parallel */

/* on master only */

MPI_Isend();

MPI_Irecv();

MPI_Waitall();

} /* end for loop */

```

masteronly style: MPI only outside of parallel regions

#### Advantages

- Simplest possible hybrid model

- Thread-parallel execution and MPI communication strictly separate

- Minimally required MPI thread support level:MPI\_THREAD\_FUNNELED

#### **Major Problems**

- All other threads are sleeping while master thread communicates!

- Only one thread per process communicating

- → possible underutilization of network bandwidth

## Masteronly style within large parallel region

```

#pragma omp parallel

for(iterations) {

#pragma omp for

for(i=0; ...) {

// ... numerics

} // barrier here

#pragma omp single

MPI Isend();

MPI Irecv();

MPI Waitall();

} // Barrier here

} /* end iter loop */

```

- Barrier before MPI required

- May be implicit

- Prevent race conditions on communication buffer data

- Between multi-threaded numerics

- and MPI access by master thread

- Enforce flush of variables

- Barrier after MPI required

- May be implicit

- Numerical loop(s) may need communicated data

## Programming models

- MPI + OpenMP

How to compile, link, and run

General considerations

> How to compile, link, and run

Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth

Memory placement on ccNUMA systems

Topology and affinity on multicore

Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

Use appropriate OpenMP compiler switch (-openmp, -fopenmp, -mp, -qsmp=openmp, ...) and MPI compiler script (if available)

- Use appropriate OpenMP compiler switch (-openmp, -fopenmp, -mp, -qsmp=openmp, ...) and MPI compiler script (if available)

- Link with MPI library

- Usually wrapped in MPI compiler script

- If required, specify to link against thread-safe MPI library

- Often automatic when OpenMP or auto-parallelization is switched on

- Use appropriate OpenMP compiler switch (-openmp, -fopenmp, -mp, -qsmp=openmp, ...) and MPI compiler script (if available)

- Link with MPI library

- Usually wrapped in MPI compiler script

- If required, specify to link against thread-safe MPI library

- Often automatic when OpenMP or auto-parallelization is switched on

- Running the code

- Highly non-portable consult system docs (if available...)

- Use appropriate OpenMP compiler switch (-openmp, -fopenmp, -mp, -qsmp=openmp, ...) and MPI compiler script (if available)

- Link with MPI library

- Usually wrapped in MPI compiler script

- If required, specify to link against thread-safe MPI library

- Often automatic when OpenMP or auto-parallelization is switched on

- Running the code

- Highly non-portable consult system docs (if available...)

- Figure out how to start fewer MPI processes than cores per node

- Use appropriate OpenMP compiler switch (-openmp, -fopenmp, -mp, -qsmp=openmp, ...) and MPI compiler script (if available)

- Link with MPI library

- Usually wrapped in MPI compiler script

- If required, specify to link against thread-safe MPI library

- Often automatic when OpenMP or auto-parallelization is switched on

- Running the code

- Highly non-portable consult system docs (if available…)

- Figure out how to start fewer MPI processes than cores per node

- Pinning (who is running where?) is extremely important → see later

## Compiling from a single source

#### Make use of pre-defined symbols

```

#ifdef OPENMP # OPENMP defined with -qopenmp

// all that is special for OpenMP

#endif

#ifdef USE MPI # USE MPI defined with -DUSE MPI

// all that is special for MPI

#endif

#ifdef USE MPI

MPI Init(...);

MPI Comm rank(..., &rank);

MPI Comm size(..., &size);

# recommended for non-MPI

#else

rank = 0:

size = 1:

#endif

```

## Compiling from a single source

#### Handling compilers

Intel MPI + Intel C

```

mpiicc -DUSE_MPI -qopenmp ...

icc -qopenmp ...

```

Intel MPI + Intel Fortran

```

mpiifort -fpp -DUSE_MPI -qopenmp ...

ifort -fpp -qopenmp ...

```

## Compiling from a single source

#### Handling compilers

Intel MPI + Intel C

```

mpiicc -DUSE_MPI -qopenmp ...

icc -qopenmp ...

```

Intel MPI + Intel Fortran

```

mpiifort -fpp -DUSE_MPI -qopenmp ...

ifort -fpp -qopenmp ...

```

OpenMPI + gcc

```

mpicc -DUSE_MPI -fopenmp ... gcc -fopenmp ...

```

OpenMPI + gfortran

```

mpif90 -cpp -DUSE_MPI -fopenmp ...

gfortran -cpp -fopenmp ...

```

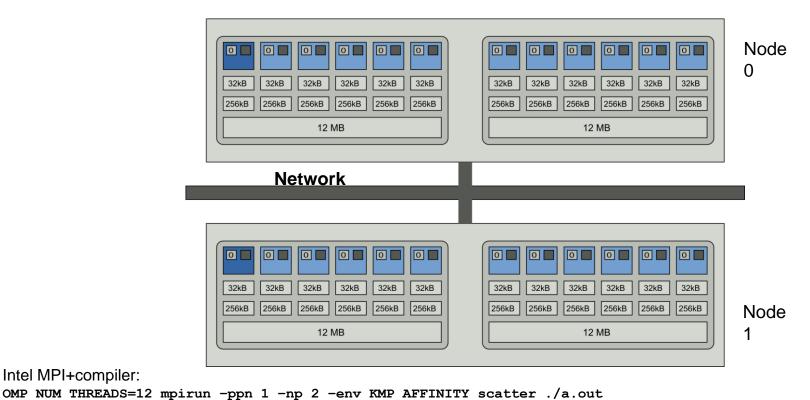

## Examples for compilation and execution

- Cray XC40 (2 NUMA domains w/ 12 cores each):

- ftn -h omp ...

- OMP\_NUM\_THREADS=12 aprun -n 4 -N 2 \

-d \$OMP\_NUM\_THREADS ./a.out

## Examples for compilation and execution

- Cray XC40 (2 NUMA domains w/ 12 cores each):

- ftn -h omp ...

- OMP\_NUM\_THREADS=12 aprun -n 4 -N 2 \

-d \$OMP\_NUM\_THREADS ./a.out

- Intel Ice Lake (36-core 2-socket) cluster, Intel MPI/OpenMP

- mpiifort -qopenmp ...

- mpirun -ppn 2 -np 4 \

- -env OMP NUM THREADS 36

- -env I MPI PIN DOMAIN socket \

- -env KMP\_AFFINITY scatter ./a.out

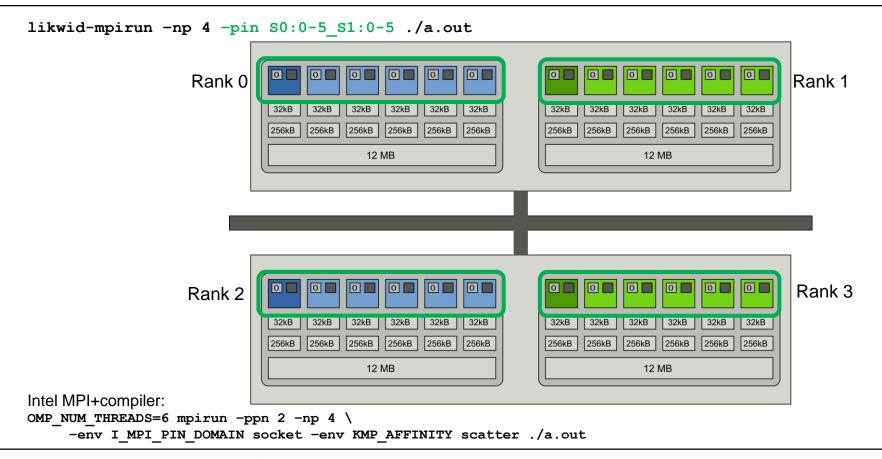

#### Examples for compilation and execution

- Cray XC40 (2 NUMA domains w/ 12 cores each):

- ftn -h omp ...

- OMP\_NUM\_THREADS=12 aprun -n 4 -N 2 \

-d \$OMP NUM THREADS ./a.out

- Intel Ice Lake (36-core 2-socket) cluster, Intel MPI/OpenMP

- mpiifort -qopenmp ...

- mpirun -ppn 2 -np 4 \

- -env OMP\_NUM\_THREADS 36

- -env I\_MPI\_PIN\_DOMAIN socket \

- -env KMP\_AFFINITY scatter ./a.out

- Intel Ice Lake (36-core 2-socket) cluster, Intel MPI/OpenMP + likwid-mpirun

- likwid-mpirun -np 4 -pin S0:0-35\_S1:0-35 ./a.out

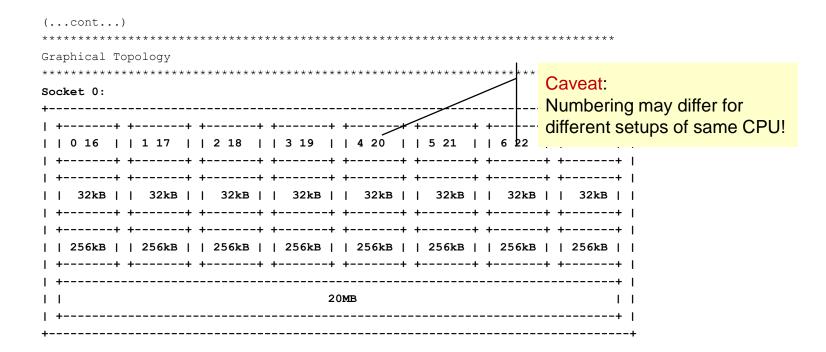

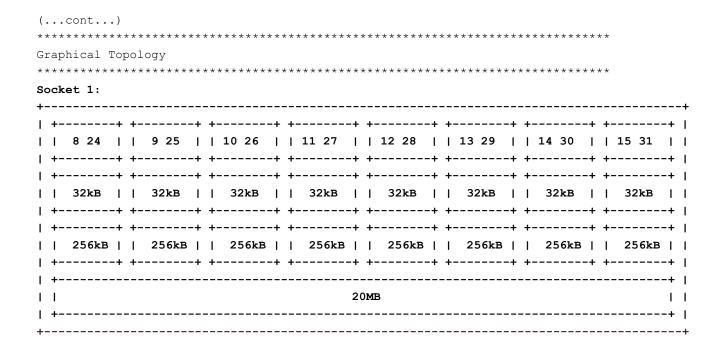

#### Learn about node topology

- A collection of tools is available

- numactl --hardware (numatools)

- lstopo --no-io (part of hwloc)

- cpuinfo -A (part of Intel MPI)

- likwid-topology (part of LIKWID tool suite <a href="http://tiny.cc/LIKWID">http://tiny.cc/LIKWID</a>)

## Learning about node topology

#### Learning about node topology

## Programming models

- MPI + OpenMP

Hands-On #1

Hello hybrid!

General considerations

How to compile, link, and run

> Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth Memory placement on ccNUMA systems

Topology and affinity on multicore

Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

#### Hands-On #1

he-hy - Hello Hybrid! - compiling, starting

- FIRST THINGS FIRST PART 1: find out about a (new) cluster login node

- 2. FIRST THINGS FIRST PART 2: find out about a (new) cluster batch jobs

- 3. MPI+OpenMP: :**TODO**: how to compile and start an application how to do conditional compilation

- 4. MPI+OpenMP: :TODO: get to know the hardware needed for pinning

# Programming models - MPI + OpenMP

System topology, ccNUMA, and memory bandwidth

General considerations

How to compile, link, and run

Hands-on: Hello hybrid!

> System topology, ccNUMA, and memory bandwidth

Memory placement on ccNUMA systems

Topology and affinity on multicore

Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

## What is "topology"?

#### Where in the machine does core (or hardware thread) #n reside?

Why is this important?

- Resource sharing (cache, data paths)

- Communication efficiency (shared vs. separate caches, buffer locality)

- Memory access locality (ccNUMA!)

#### Compute nodes – caches

#### Compute nodes – caches

| Latency | ← typical → | Bandwidth           |

|---------|-------------|---------------------|

| 1–2 ns  | L1 cache    | 200 GB/s            |

| 3–10 ns | L2/L3 cache | 50 GB/s             |

| 100 ns  | memory      | 20 GB/s<br>(1 core) |

#### Ping-Pong Benchmark – Latency

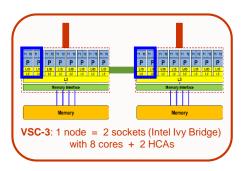

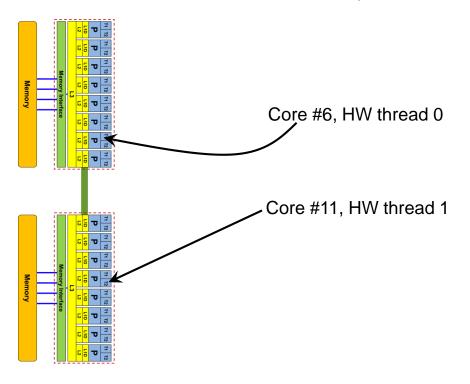

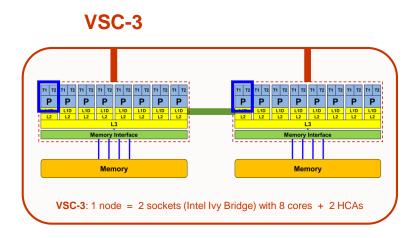

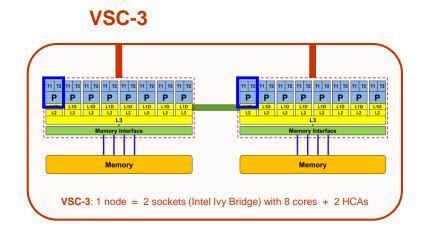

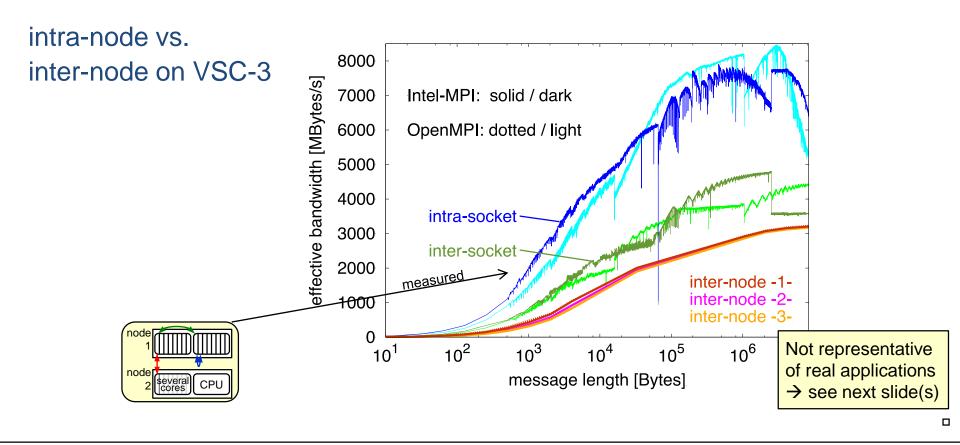

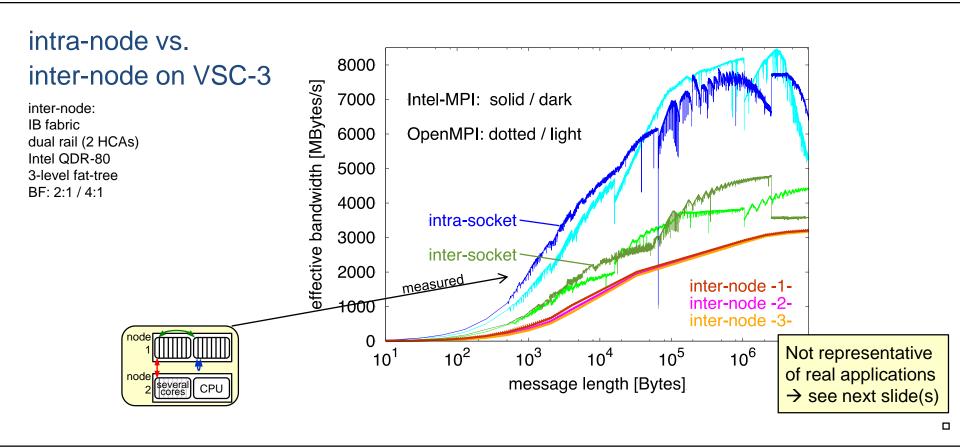

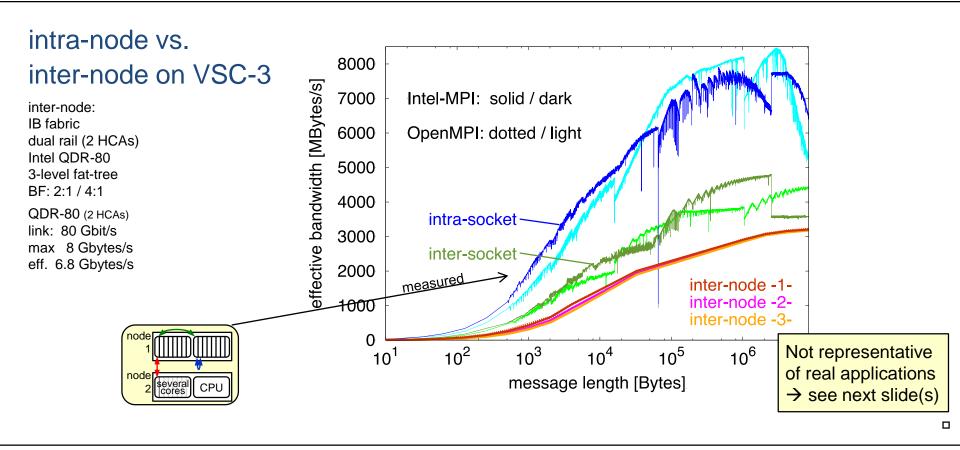

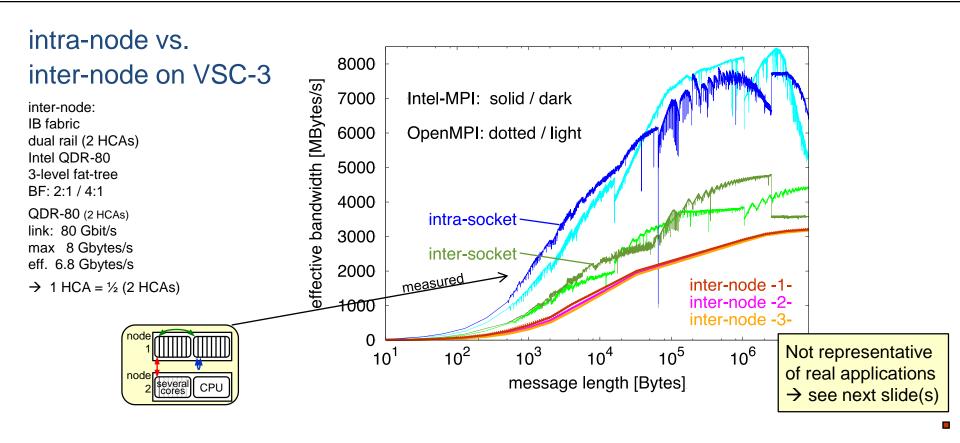

#### Intra-node vs. inter-node on VSC-3

- nodes = 2 sockets (Intel Ivy Bridge) with 8 cores + 2 HCAs

- inter-node = IB fabric = dual rail Intel QDR-80 = 3-level fat-tree (BF: 2:1 / 4:1)

```

myID = get process ID()

if (myID.eq.0) then

targetID = 1

S = get walltime()

call Send message(buffer,N,targetID)

call Receive message(buffer,N,targetID)

E = get walltime()

GBYTES = 2*N/(E-S)/1.d9 ! Gbyte/s rate

TIME = (E-S)/2*1.d6 ! transfer time

else

targetID = 0

call Receive message(buffer,N,targetID)

call Send message(buffer,N,targetID)

endif

```

#### Ping-Pong Benchmark – Latency

#### Intra-node vs. inter-node on VSC-3

- nodes = 2 sockets (Intel Ivy Bridge) with 8 cores + 2 HCAs

- inter-node = IB fabric = dual rail Intel QDR-80 = 3-level fat-tree (BF: 2:1 / 4:1)

```

myID = get process ID()

if (myID.eq.0) then

targetID = 1

S = get walltime()

call Send message(buffer,N,targetID)

call Receive message (buffer, N, targetID)

E = get walltime()

GBYTES = 2*N/(E-S)/1.d9 ! Gbyte/s rate

TIME = (E-S)/2*1.d6 ! transfer time

else

targetID = 0

call Receive message(buffer,N,targetID)

call Send message(buffer,N,targetID)

endif

```

| Latency<br>[µs] | MPI_Send() |           |

|-----------------|------------|-----------|

|                 | OpenMPI    | Intel MPI |

| intra-socket    | 0.3 µs     | 0.3 µs    |

| inter-socket    | 0.6 µs     | 0.7 µs    |

| IB -1- edge     | 1.2 µs     | 1.4 µs    |

| IB -2- leaf     | 1.6 µs     | 1.8 µs    |

| IB -3- spine    | 2.1 µs     | 2.3 µs    |

| For comparison:<br>typical latencies |         |  |

|--------------------------------------|---------|--|

| L1 cache                             | 1–2 ns  |  |

| L2/L3 c.                             | 3–10 ns |  |

| memory                               | 100 ns  |  |

| HPC<br>networks                      | 1–10 µs |  |

#### Ping-Pong Benchmark – Latency

#### Intra-node vs. inter-node on VSC-3

- nodes = 2 sockets (Intel Ivy Bridge) with 8 cores + 2 HCAs

- inter-node = IB fabric = dual rail Intel QDR-80 = 3-level fat-tree (BF: 2:1 / 4:1)

```

myID = get process ID()

if (myID.eq.0) then

targetID = 1

S = get walltime()

call Send message(buffer,N,targetID)

call Receive message (buffer, N, targetID)

E = get walltime()

GBYTES = 2*N/(E-S)/1.d9 ! Gbyte/s rate

TIME = (E-S)/2*1.d6 ! transfer time

else

targetID = 0

call Receive message(buffer,N,targetID)

call Send message(buffer,N,targetID)

endif

```

| Latency      | MPI_Send() |           |

|--------------|------------|-----------|

| [µs]         | OpenMPI    | Intel MPI |

| intra-socket | 0.3 µs     | 0.3 µs    |

| inter-socket | 0.6 µs     | 0.7 μs    |

| IB -1- edge  | 1.2 µs     | 1.4 µs    |

| IB -2- leaf  | 1.6 µs     | 1.8 µs    |

| IB -3- spine | 2.1 µs     | 2.3 µs    |

| For comparison: typical latencies |         |  |

|-----------------------------------|---------|--|

| L1 cache                          | 1–2 ns  |  |

| L2/L3 c.                          | 3–10 ns |  |

| memory                            | 100 ns  |  |

| HPC<br>networks                   | 1–10 µs |  |

→ Avoiding slow data paths is the key to most performance optimizations!

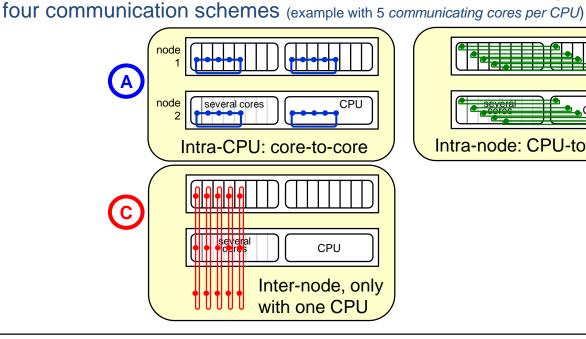

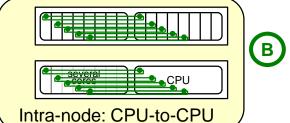

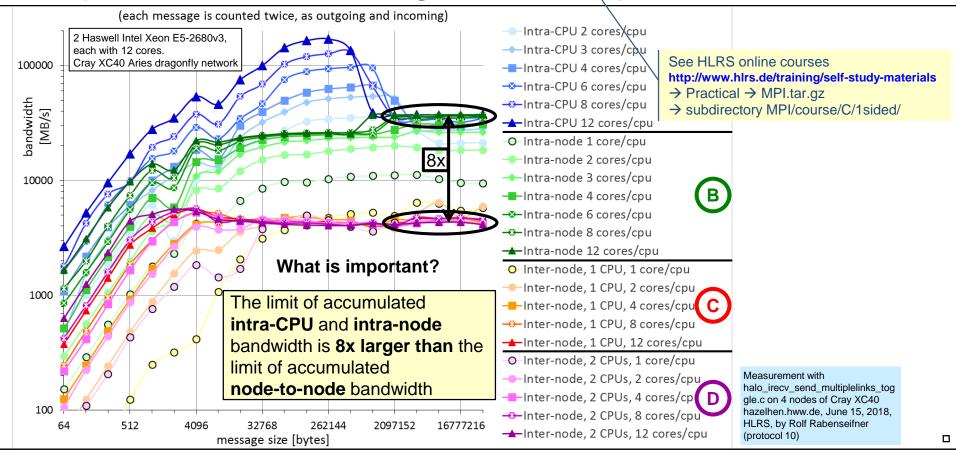

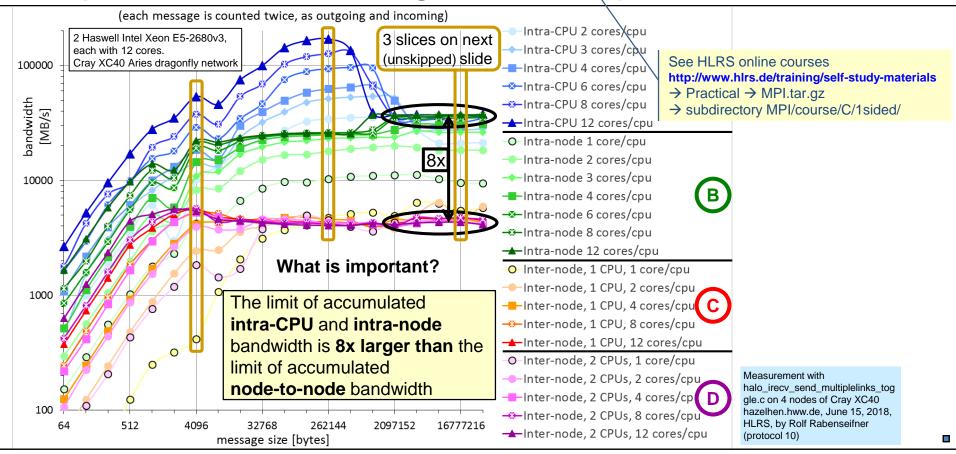

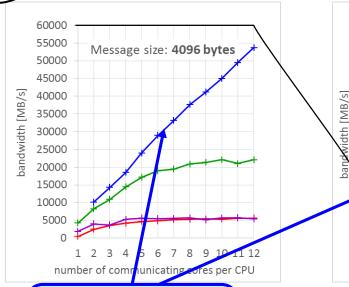

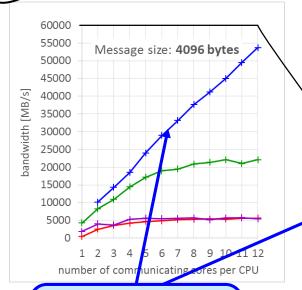

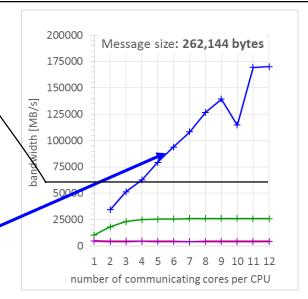

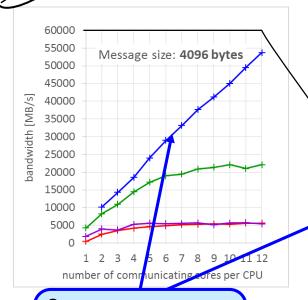

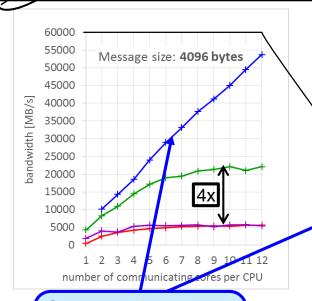

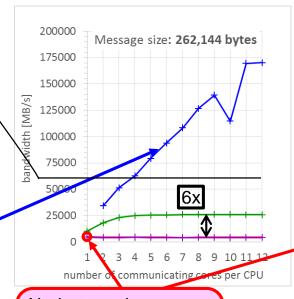

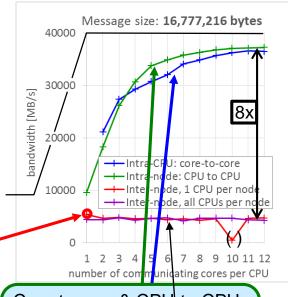

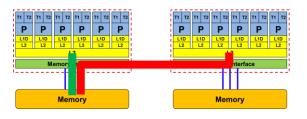

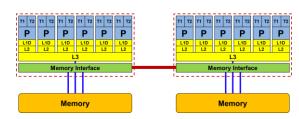

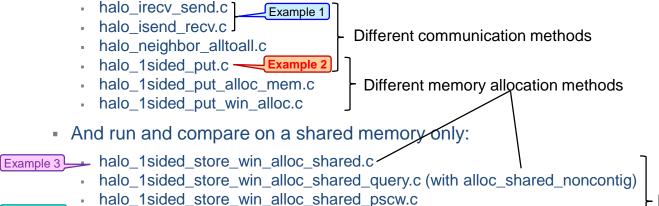

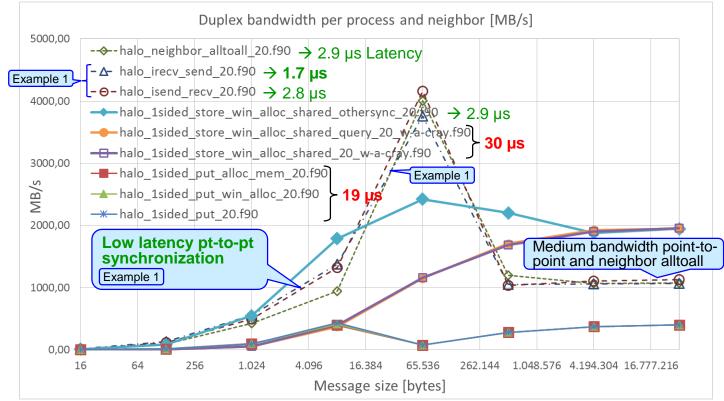

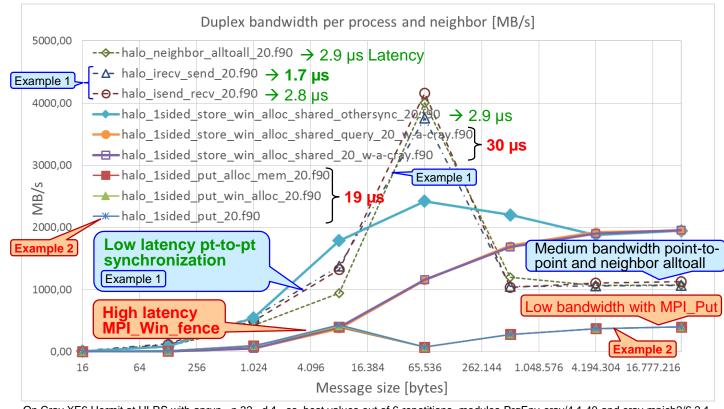

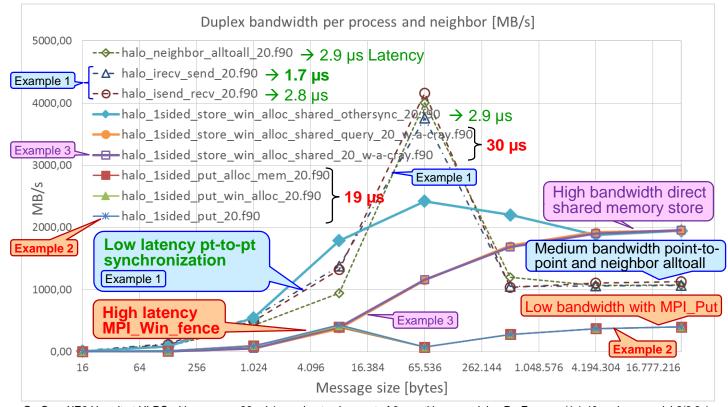

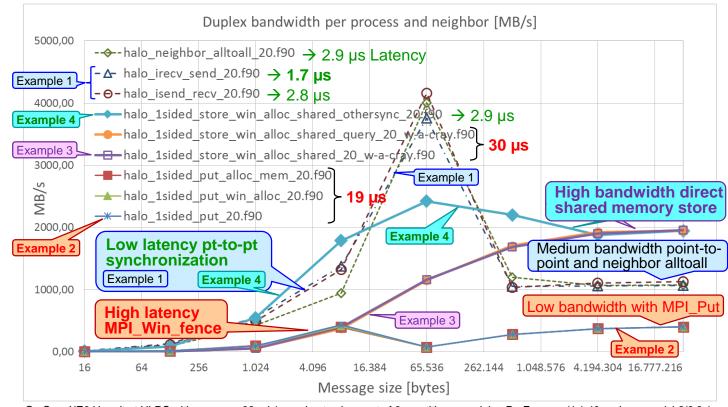

Benchmark halo\_irecv\_send\_multiplelinks\_toggle.c

- Varying message size,

- number of communication cores per CPU, and

- four communication schemes (example with 5 communicating cores per CPU)

node several cores CPU

Intra-CPU: core-to-core

See HLRS online courses

http://www.hlrs.de/training/self-study-materials

→ Practical → MPI.tar.gz

→ subdirectory MPI/course/C/1sided/

Benchmark halo irecv send multiplelinks toggle.c

- Varying message size,

- number of communication cores per CPU, and

- four communication schemes (example with 5 communicating cores per CPU)

See HLRS online courses http://www.hlrs.de/training/self-study-materials

- → Practical → MPI.tar.gz

- → subdirectory MPI/course/C/1sided/

Benchmark halo irecv send multiplelinks toggle.c

- Varying message size,

- number of communication cores per CPU, and

See HLRS online courses http://www.hlrs.de/training/self-study-materials

- → Practical → MPI.tar.gz

- → subdirectory MPI/course/C/1sided/

Benchmark halo irecv send multiplelinks toggle.c

- Varying message size,

- number of communication cores per CPU, and

See HLRS online courses http://www.hlrs.de/training/self-study-materials

- → Practical → MPI.tar.gz

- → subdirectory MPI/course/C/1sided/

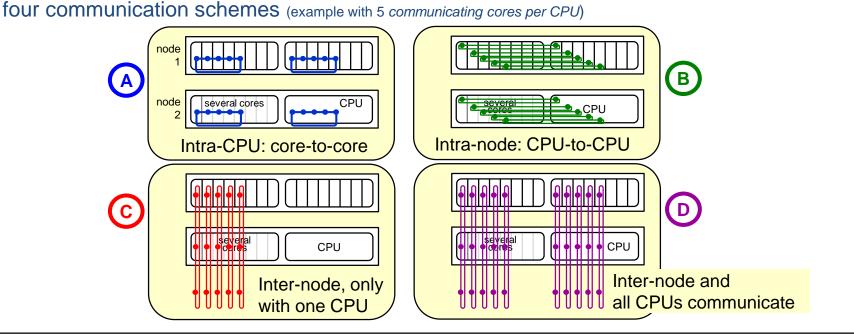

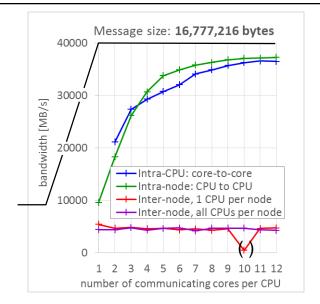

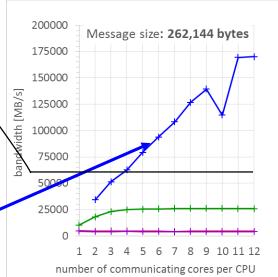

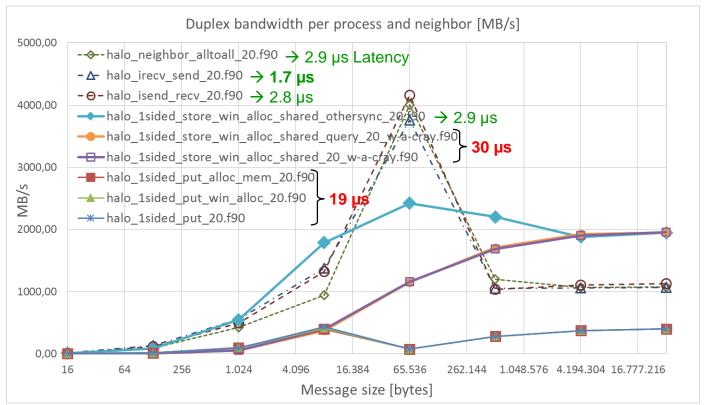

## Duplex accumulated ring bandwidth per node

## Duplex accumulated ring bandwidth per node

## Duplex accumulated ring bandwidth per node

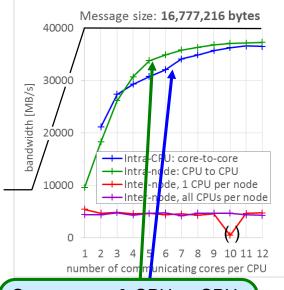

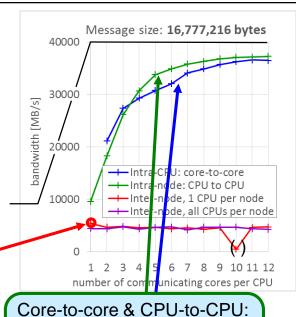

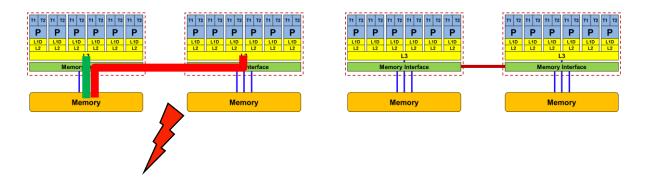

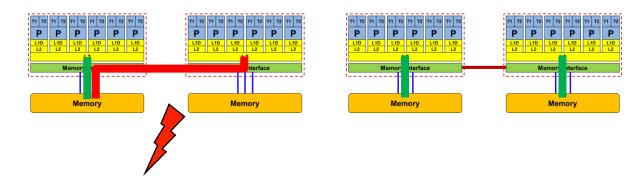

## cumulated – scaling vs. asymptotic behavior

## cumulated – scaling vs. asymptotic behavior

<u>Core-to-core:</u> Linear scaling for small to medium size mes-

sages due to caches

## cumulated – scaling vs. asymptotic behavior

<u>Core-to-core:</u>

Linear scaling for small to medium size messages due to caches

Core-to-core & CPU-to-CPU:

Long messages:

Same asymptotic limit

through memory bandwidth

## cumulated – scaling vs. asymptotic behavior

Core-to-core:

Linear scaling for small to medium size messages due to caches

Node-to-node:

One duplex link by

one core already fully

saturates the network

Long messages:

Same asymptotic limit

through memory bandwidth

١

### Cumulated – scaling vs. asymptotic behavior

Core-to-core:

Linear scaling for small

to medium size messages due to caches

Node-to-node:

One duplex link by

one core already fully

saturates the network

Core-to-core & CPU-to-CPU:

Long messages:

Same asymptotic limit

through memory bandwidth

Result: The limit of accumulated **intra-CPU** and **intra-node** bandwidth is **8x larger than** the limit of accumulated **node-to-node** bandwidth

Rolf Rabenseifner (HLRS), Georg Hager (NHR@FAU), Claudia Blaas-Schenner (

39/239

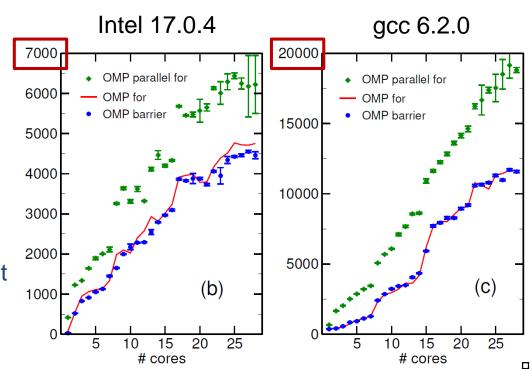

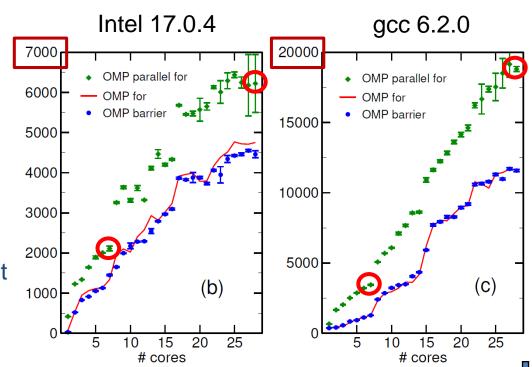

## OpenMP barrier synchronization cost

Comparison of barrier synchronization cost with increasing number of threads

- 2x Haswell 14-core (CoD mode)

- Optimistic measurements (repeated 1000s of times)

- No impact from previous activity in cache

- → Barrier sync time highly dependent on system topology & OpenMP runtime implementation

## OpenMP barrier synchronization cost

Comparison of barrier synchronization cost with increasing number of threads

- 2x Haswell 14-core (CoD mode)

- Optimistic measurements (repeated 1000s of times)

- No impact from previous activity in cache

- → Barrier sync time highly dependent on system topology & OpenMP runtime implementation

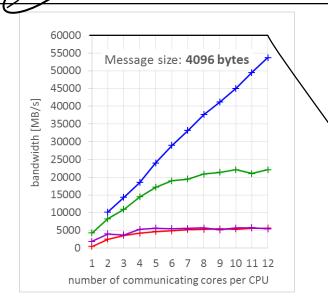

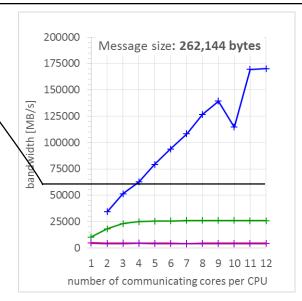

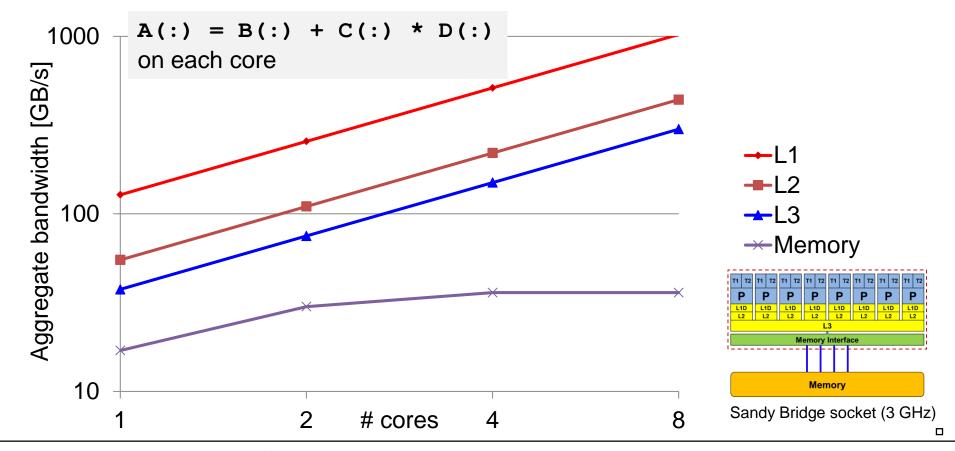

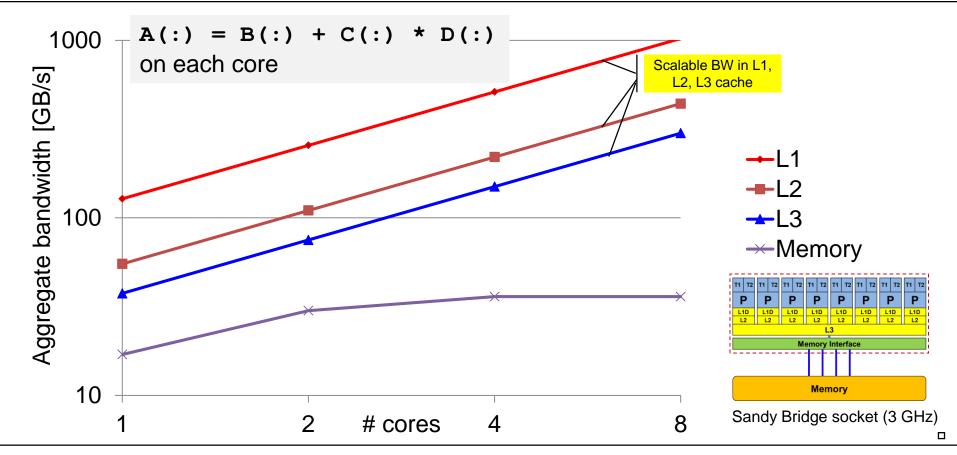

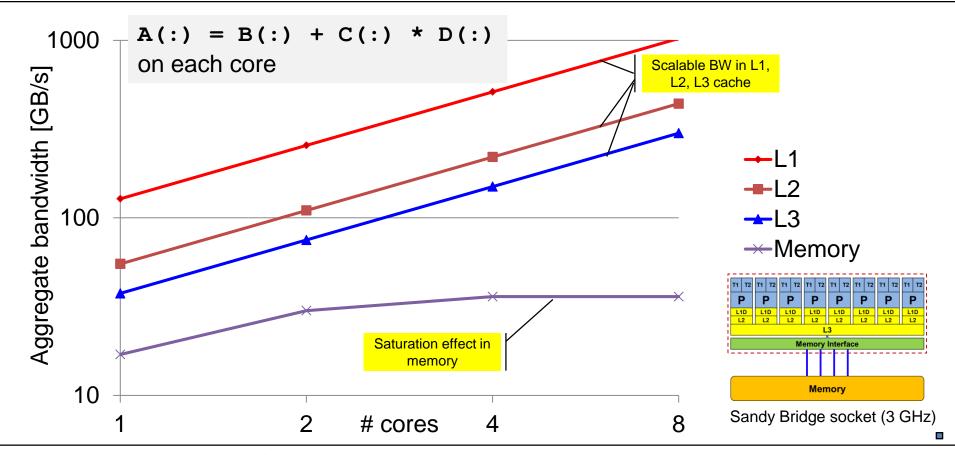

### Accumulated bandwidth saturation vs. # cores

Rolf Rabenseifner (HLRS), Georg Hager (NHR@FAU), Claudia Blaas-Schenner (VSC, TU Wien)

#### Accumulated bandwidth saturation vs. # cores

Rolf Rabenseifner (HLRS), Georg Hager (NHR@FAU), Claudia Blaas-Schenner (VSC, TU Wien)

#### Accumulated bandwidth saturation vs. # cores

Rolf Rabenseifner (HLRS), Georg Hager (NHR@FAU), Claudia Blaas-Schenner (VSC, TU Wien)

# Programming models

- MPI + OpenMP

Memory placement on ccNUMA systems

General considerations

How to compile, link, and run

Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth

> Memory placement on ccNUMA systems

Topology and affinity on multicore

Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

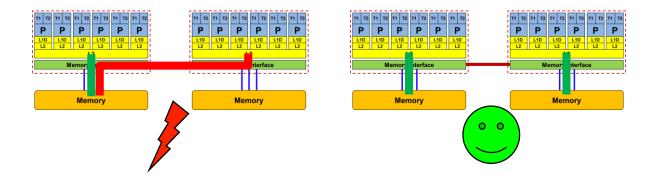

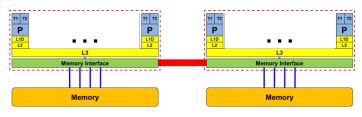

#### ccNUMA:

- whole memory is transparently accessible by all processors

- but physically distributed

- with varying bandwidth and latency

- and potential contention (shared memory paths)

- Memory placement occurs with OS page granularity (often 4 KiB)

- whole memory is transparently accessible by all processors

- but physically distributed

- with varying bandwidth and latency

- and potential contention (shared memory paths)

- Memory placement occurs with OS page granularity (often 4 KiB)

#### ccNUMA:

- whole memory is transparently accessible by all processors

- but physically distributed

- with varying bandwidth and latency

- and potential contention (shared memory paths)

- Memory placement occurs with OS page granularity (often 4 KiB)

- whole memory is transparently accessible by all processors

- but physically distributed

- with varying bandwidth and latency

- and potential contention (shared memory paths)

- Memory placement occurs with OS page granularity (often 4 KiB)

- whole memory is transparently accessible by all processors

- but physically distributed

- with varying bandwidth and latency

- and potential contention (shared memory paths)

- Memory placement occurs with OS page granularity (often 4 KiB)

- whole memory is transparently accessible by all processors

- but physically distributed

- with varying bandwidth and latency

- and potential contention (shared memory paths)

- Memory placement occurs with OS page granularity (often 4 KiB)

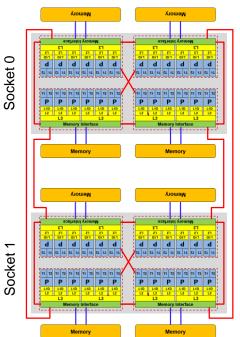

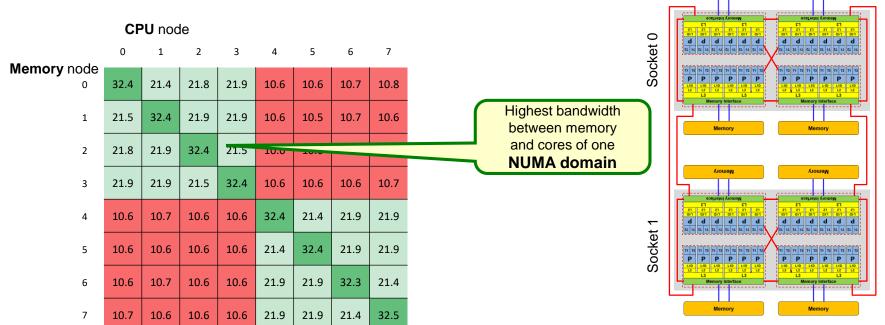

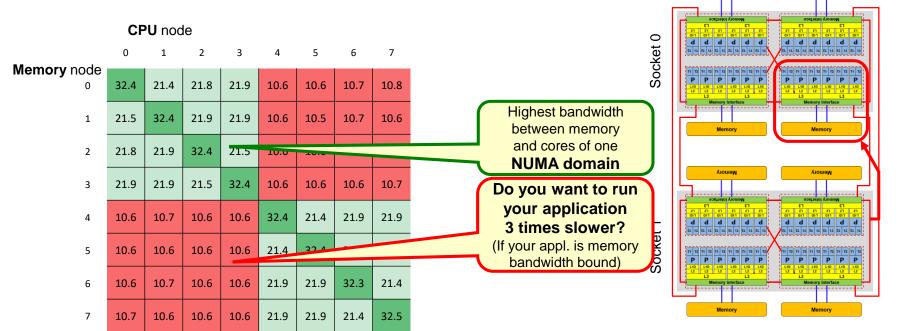

#### How much bandwidth does non-local access cost?

Example: AMD "Naples" 2-socket system (8 chips, 2 sockets, 48 cores):

STREAM Triad bandwidth measurements [Gbyte/s]

|             | <b>CPU</b> node |      |      |      |      |      |      |      |

|-------------|-----------------|------|------|------|------|------|------|------|

|             | 0               | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

| Memory node | 32.4            | 21.4 | 21.8 | 21.9 | 10.6 | 10.6 | 10.7 | 10.8 |

| 1           | 21.5            | 32.4 | 21.9 | 21.9 | 10.6 | 10.5 | 10.7 | 10.6 |

| 2           | 21.8            | 21.9 | 32.4 | 21.5 | 10.6 | 10.6 | 10.8 | 10.7 |

| 3           | 21.9            | 21.9 | 21.5 | 32.4 | 10.6 | 10.6 | 10.6 | 10.7 |

| 4           | 10.6            | 10.7 | 10.6 | 10.6 | 32.4 | 21.4 | 21.9 | 21.9 |

| 5           | 10.6            | 10.6 | 10.6 | 10.6 | 21.4 | 32.4 | 21.9 | 21.9 |

| 6           | 10.6            | 10.7 | 10.6 | 10.6 | 21.9 | 21.9 | 32.3 | 21.4 |

| 7           | 10.7            | 10.6 | 10.6 | 10.6 | 21.9 | 21.9 | 21.4 | 32.5 |

#### How much bandwidth does non-local access cost?

Example: AMD "Naples" 2-socket system (8 chips, 2 sockets, 48 cores):

STREAM Triad bandwidth measurements [Gbyte/s]

#### How much bandwidth does non-local access cost?

■ Example: AMD "Naples" 2-socket system (8 chips, 2 sockets, 48 cores):

STREAM Triad bandwidth measurements [Gbyte/s]

## Avoiding locality problems

- How can we make sure that memory ends up where it is close to the CPU that uses it?

- See next slides (first-touch initialization)

- How can we make sure that it stays that way throughout program execution?

- See later in the tutorial (pinning)

Taking control is the key strategy!

### Solving Memory Locality Problems: First Touch

"Golden Rule" of ccNUMA:

A memory page gets mapped into the local memory of the processor that first touches it!

- Consequences

- Process/thread-core affinity is decisive!

- With OpenMP, data initialization code becomes important even if it takes little time to execute ("parallel first touch")

- Parallel first touch is automatic for pure MPI

- If thread team does not span across NUMA domains, memory mapping is not a problem

- Automatic page migration may help if memory is used long enough

### Solving Memory Locality Problems: First Touch

"Golden Rule" of ccNUMA:

A memory page gets mapped into the local memory of the processor that first touches it!

- Except if there is not enough local memory available

- Some OSs allow to influence placement in more direct ways

- → libnuma (Linux)

- Caveat: "touch" means "write," not "allocate" or "read"

### Solving Memory Locality Problems: First Touch

"Golden Rule" of ccNUMA:

A memory page gets mapped into the local memory of the processor that first touches it!

- Except if there is not enough local memory available

- Some OSs allow to influence placement in more direct ways

- → libnuma (Linux)

- Caveat: "touch" means "write," not "allocate" or "read"

- Example:

```

double *huge = (double*)malloc(N*sizeof(double));

// memory not mapped yet

for(i=0; i<N; i++) // or i+=PAGE_SIZE

huge[i] = 0.0; // mapping takes place here!</pre>

```

### Most simple case: explicit initialization

```

integer,parameter :: N=1000000

double precision A(N), B(N)

A=0.d0

!$OMP parallel do

do i = 1, N

B(i) = function (A(i))

end do

!$OMP end parallel do

```

ſ

### Most simple case: explicit initialization

```

integer,parameter :: N=10000000

double precision A(N), B(N)

A=0.d0

!$OMP parallel do

do i = 1, N

B(i) = function (A(i))

end do

!$OMP end parallel do

```

```

integer, parameter :: N=10000000

double precision A(N),B(N)

!$OMP parallel

!$OMP do schedule(static)

do i = 1, N

A(i) = 0.d0

end do

!$OMP end do

!$OMP do schedule(static)

do i = 1, N

B(i) = function (A(i))

end do

!SOMP end do

!$OMP end parallel

```

## Handling ccNUMA in practice

- Solution A

- One (or more) MPI process(es) per ccNUMA domain

- Pro: optimal page placement (perfectly local memory access) for free

- Con: higher number (>1) of MPI processes on each node

## Handling ccNUMA in practice

- Solution A

- One (or more) MPI process(es) per ccNUMA domain

- Pro: optimal page placement (perfectly local memory access) for free

- Con: higher number (>1) of MPI processes on each node

- Solution B

- One MPI process per node or one MPI process spans multiple ccNUMA domains

- Pro: Smaller number of MPI processes compared to Solution A

- Cons:

- Explicitly parallel initialization needed to "bind" the data to each ccNUMA domain

→ otherwise loss of performance

- Dynamic/guided schedule or tasking → loss of performance

## Handling ccNUMA in practice

- Solution A

- One (or more) MPI process(es) per ccNUMA domain

- Pro: optimal page placement (perfectly local memory access) for free

- Con: higher number (>1) of MPI processes on each node

- Solution B

- One MPI process per node or one MPI process spans multiple ccNUMA domains

- Pro: Smaller number of MPI processes compared to Solution A

- Cons:

- Explicitly parallel initialization needed to "bind" the data to each ccNUMA domain

→ otherwise loss of performance

- Dynamic/guided schedule or tasking → loss of performance

- Thread binding is mandatory for A and B! Never trust the defaults!

### Conclusions from the observed topology effects

- Know your hardware characteristics:

- Hardware topology (use tools such as likwid-topology)

- Typical hardware bottlenecks

- These are independent of the programming model!

- Hardware bandwidths, latencies, peak performance numbers

### Conclusions from the observed topology effects

- Know your hardware characteristics:

- Hardware topology (use tools such as likwid-topology)

- Typical hardware bottlenecks

- These are independent of the programming model!

- Hardware bandwidths, latencies, peak performance numbers

- Know your software characteristics

- Typical numbers for communication latencies, bandwidths

- Typical OpenMP overheads

### Conclusions from the observed topology effects

- Know your hardware characteristics:

- Hardware topology (use tools such as likwid-topology)

- Typical hardware bottlenecks

- These are independent of the programming model!

- Hardware bandwidths, latencies, peak performance numbers

- Know your software characteristics

- Typical numbers for communication latencies, bandwidths

- Typical OpenMP overheads

- Learn how to take control

- See next chapter on affinity control

- Leveraging topology effects is a part of code optimization!

# Programming models

## - MPI + OpenMP

### Topology and affinity on multicore

General considerations

How to compile, link, and run

Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth Memory placement on ccNUMA systems

#### > Topology and affinity on multicore

Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

- Highly OS-dependent system calls

- But available on all OSs

- Non-portable

L

- Highly OS-dependent system calls

- But available on all OSs

- Non-portable

- Support for user-defined pinning for OpenMP threads in all compilers

- Compiler specific

- Standardized in OpenMP (places)

- Generic Linux: taskset, numactl, likwid-pin

- Highly OS-dependent system calls

- But available on all OSs

- Non-portable

- Support for user-defined pinning for OpenMP threads in all compilers

- Compiler specific

- Standardized in OpenMP (places)

- Generic Linux: taskset, numactl, likwid-pin

- Affinity awareness in all MPI libraries

- Not defined by the MPI standard (as of 4.0)

- Necessarily non-portable feature of the startup mechanism (mpirun, ...)

- Highly OS-dependent system calls

- But available on all OSs

- Non-portable

- Support for user-defined pinning for OpenMP threads in all compilers

- Compiler specific

- Standardized in OpenMP (places)

- Generic Linux: taskset, numactl, likwid-pin

- Affinity awareness in all MPI libraries

- Not defined by the MPI standard (as of 4.0)

- Necessarily non-portable feature of the startup mechanism (mpirun, ...)

- Affinity awareness in batch scheduler

- Batch scheduler must work with MPI + OpenMP affinity

- Difficult, non-portable, every combination is different

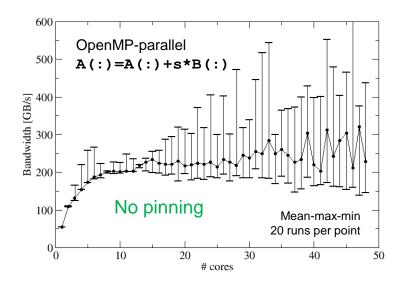

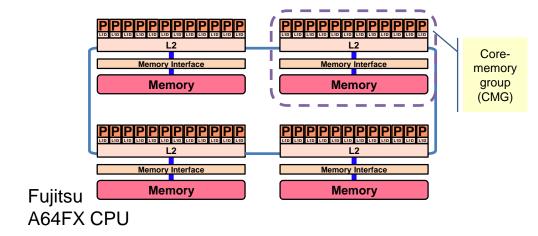

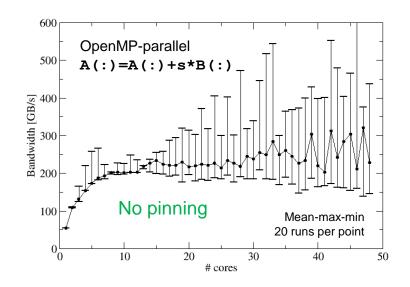

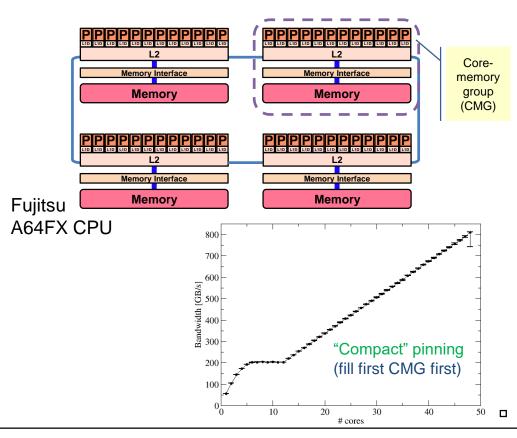

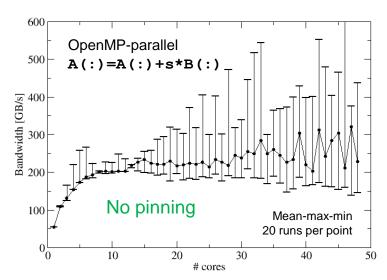

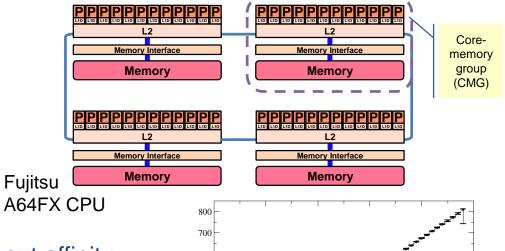

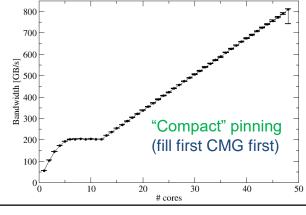

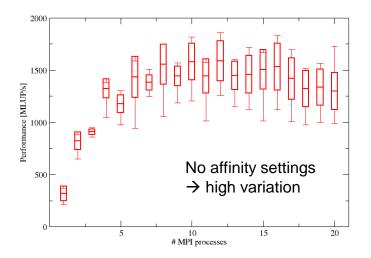

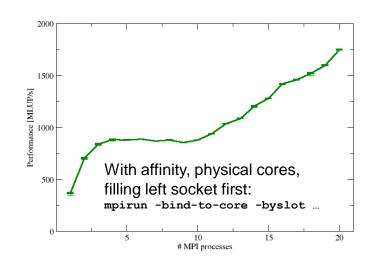

# Anarchy vs. affinity with OpenMP STREAM

# Anarchy vs. affinity with OpenMP STREAM

# Anarchy vs. affinity with OpenMP STREAM

There are several reasons for caring about affinity:

- Eliminating performance variation

- Making use of architectural features

- Avoiding resource contention

A place consists of one or more processors.

Pinning on the level of places.

Free migration of the threads on a place between the processors of that place.

A place consists of one or more processors.

Pinning on the level of places.

Free migration of the threads on a place between the processors of that place.

- OMP\_PLACES=threads

- → Each place corresponds to the single *processor* of a single hardware thread (hyper-thread)

abstract name

- OMP\_PLACES=cores

- → Each place corresponds to the processors (one or more hardware threads) of a single core

- OMP\_PLACES=sockets

- → Each place corresponds to the processors of a single socket (consisting of all hardware threads of one or more cores)

- OMP\_PLACES=abstract\_name(num\_places)

- → In general, the number of places may be explicitly defined

A *place* consists of one or more *processors*.

Pinning on the level of *places*.

Free migration of the threads on a place between the *processors* of that place.

- OMP\_PLACES=threads

- → Each place corresponds to the single *processor* of a single hardware thread (hyper-thread)

abstract name

- OMP\_PLACES=cores

- → Each place corresponds to the processors (one or more hardware threads) of a single core

- OMP\_PLACES=sockets

- → Each place corresponds to the processors of a single socket (consisting of all hardware threads of one or more cores)

- OMP\_PLACES=abstract\_name(num\_places)

- → In general, the number of places may be explicitly defined

- Or with explicit numbering, e.g. 8 places, each consisting of 4 processors:

- setenv OMP PLACES "{0,1,2,3},{4,5,6,7},{8,9,10,11}, ... {28,29,30,31}"

- setenv OMP\_PLACES "{0:4},{4:4},{8:4}, ... {28:4}"

- setenv OMP\_PLACES "{0:4}:8:4"

A place consists of one or more processors.

processor is the smallest unit to run a thread or task

Free migration of the threads on a place between the *processors* of that place.

- OMP\_PLACES=threads

- abstract\_name

- → Each place corresponds to the single *processor* of a single hardware thread (hyper-thread)

- OMP\_PLACES=cores

Pinning on the level of *places*.

- → Each place corresponds to the processors (one or more hardware threads) of a single core

- OMP PLACES=sockets

- → Each place corresponds to the processors of a single socket (consisting of all hardware threads of one or more cores)

<lower-bound>:<number of entries>[:<stride>]

- OMP\_PLACES=abstract\_name(num\_places)

- → In general, the number of places may be explicitly defined

- Or with explicit numbering, e.g. 8 places, each consting of 4 processors:

- setenv OMP\_PLACES "{0,1,2,3},{4,5,6,7},{8,9,10,11}, ... {28,29,30,31}"

- setenv OMP PLACES "{0:4},{4:4},{8:4}, ... {28:4}"

- setenv OMP PLACES "{0:4}:8:4"

A place consists of one or more processors.

processor is the smallest unit to run a thread or task

Free migration of the threads on a place between the *processors* of that place.

- OMP PLACES=threads

- abstract name

- → Each place corresponds to the single *processor* of a single hardware thread (hyper-thread)

- OMP PLACES=cores

Pinning on the level of *places*.

- → Each place corresponds to the processors (one or more hardware threads) of a single core

- OMP PLACES=sockets

- → Each place corresponds to the processors of a single socket (consisting of all hardware threads of one or more cores)

<lower-bound>:<number of entries>[:<stride>]

- OMP PLACES=abstract\_name(num\_places)

- → In general, the number of places may be explicitly defined

- Or with explicit numbering, e.g. 8 places, each consisting of 4 processors:

- setenv OMP\_PLACES "{0,1,2,3},{4,5,6,7},{8,9,10,11}, ... {28,29,

- setenv OMP PLACES "{0:4},{4:4},{8:4}, ... {28:4}"

- setenv OMP PLACES "{0:4}:8:4"

#### CAUTION:

The numbers highly depend on hardware and operating system, e.g., {0,1} = hyper-threads of 1st core of 1st socket, or  $\{0,1\} = 1^{st}$  hyper-thread of  $1^{st}$  core of 1st and 2nd socket, or ...

## OMP\_PROC\_BIND variable / proc\_bind() clause

#### Determines how places are used for pinning:

|                  | OMP_PROC_BIND | Meaning                                                                                                     |

|------------------|---------------|-------------------------------------------------------------------------------------------------------------|

| Used for         | FALSE         | Affinity disabled                                                                                           |

|                  | TRUE          | Affinity enabled, implementation defined strategy                                                           |

|                  | CLOSE         | Threads bind to consecutive places                                                                          |

|                  | SPREAD        | Threads are evenly scattered among places                                                                   |

|                  | MASTER        | Threads bind to the same place as the master thread that was running before the parallel region was entered |

| nested<br>OpenMP |               |                                                                                                             |

Intel Xeon w/ SMT, 2x36 cores, 1 thread per physical core, fill 1 socket

```

OMP_NUM_THREADS=36

OMP_PLACES=cores

OMP_PROC_BIND=close

```

Intel Xeon w/ SMT, 2x36 cores, 1 thread per physical core, fill 1 socket

```

OMP_NUM_THREADS=36

OMP_PLACES=cores

OMP_PROC_BIND=close

```

Intel Xeon Phi with 72 cores,

32 cores to be used, 2 threads per physical core

```

OMP_NUM_THREADS=64

OMP_PLACES=cores(32)

OMP_PROC_BIND=close  # spread will also do

```

Intel Xeon w/ SMT, 2x36 cores, 1 thread per physical core, fill 1 socket

```

OMP_NUM_THREADS=36

OMP_PLACES=cores

OMP_PROC_BIND=close

```

Intel Xeon Phi with 72 cores,

32 cores to be used, 2 threads per physical core

```

OMP_NUM_THREADS=64

OMP_PLACES=cores(32)

OMP_PROC_BIND=close  # spread will also do

```

Intel Xeon, 2 sockets, 4 threads per socket (no binding within socket!)

```

OMP_NUM_THREADS=8

OMP_PLACES=sockets

OMP_PROC_BIND=close  # spread will also do

```

• Intel Xeon w/ SMT, 2x36 cores, 1 thread per physical core, fill 1 socket

```

OMP_NUM_THREADS=36

OMP_PLACES=cores

OMP_PROC_BIND=close

```

Intel Xeon Phi with 72 cores,

32 cores to be used, 2 threads per physical core

```

OMP_NUM_THREADS=64

OMP_PLACES=cores(32)

OMP_PROC_BIND=close  # spread will also do

```

Intel Xeon, 2 sockets, 4 threads per socket (no binding within socket!)

```

OMP_NUM_THREADS=8

OMP_PLACES=sockets

OMP_PROC_BIND=close  # spread will also do

```

Intel Xeon, 2 sockets, 4 threads per socket, binding to cores

```

OMP_NUM_THREADS=8

OMP_PLACES=cores

OMP_PROC_BIND=spread

```

Intel Xeon w/ SMT, 2x36 cores, 1 thread per physical core, fill 1 socket

```

OMP_NUM_THREADS=36

OMP_PLACES=cores

OMP_PROC_BIND=close

```

Intel Xeon Phi with 72 cores,

32 cores to be used, 2 threads per physical core

```

OMP_NUM_THREADS=64

OMP_PLACES=cores(32)

OMP_PROC_BIND=close  # spread will also do

```

Intel Xeon, 2 sockets, 4 threads per socket (no binding within socket!)

```

OMP_NUM_THREADS=8

OMP_PLACES=sockets

OMP_PROC_BIND=close  # spread will also do

```

Intel Xeon, 2 sockets, 4 threads per socket, binding to cores

```

OMP_NUM_THREADS=8

OMP_PLACES=cores

OMP_PROC_BIND=spread

```

Always prefer abstract places instead of HW thread IDs!

# Pinning of MPI processes

- Highly system dependent!

- Intel MPI: env variable I\_MPI\_PIN\_DOMAIN

- OpenMPI: choose between several mpirun options, e.g.,

-bind-to-core, -bind-to-socket, -bycore, -byslot ...

- Cray's aprun: pinning by default

Platform-independent tools: likwid-mpirun (likwid-pin, numactl)

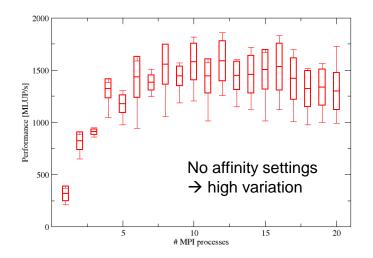

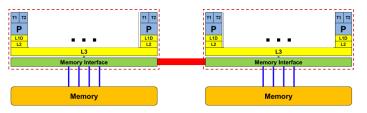

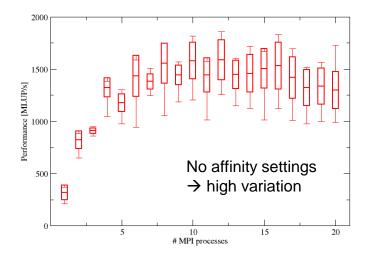

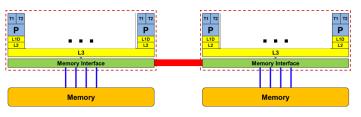

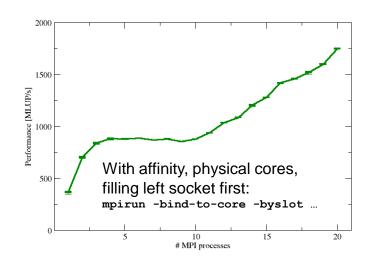

## Anarchy vs. affinity with a heat equation solver

2x 10-core Intel Ivy Bridge, OpenMPI

## Anarchy vs. affinity with a heat equation solver

2x 10-core Intel Ivy Bridge, OpenMPI

## Anarchy vs. affinity with a heat equation solver

#### Reasons for caring about affinity:

- Eliminating performance variation

- Making use of architectural features

- Avoiding resource contention

2x 10-core Intel Ivy Bridge, OpenMPI

#### likwid-mpirun: 1 MPI process per node

likwid-mpirun -np 2 -pin N:0-11 ./a.out

Rolf Rabenseifner (HLRS), Georg Hager (NHR@FAU), Claudia Blaas-Schenner (VSC, TU Wien)

Intel MPI+compiler:

#### likwid-mpirun: 1 MPI process per socket

- Learn how to take control of hybrid execution!

- Almost all performance features depend on topology and thread placement! (especially if SMT/Hyperthreading is on)

- Learn how to take control of hybrid execution!

- Almost all performance features depend on topology and thread placement! (especially if SMT/Hyperthreading is on)

- Always observe the topology dependence of

- Intranode MPI performance

- OpenMP overheads

- Saturation effects / scalability behavior with bandwidth-bound code

- Learn how to take control of hybrid execution!

- Almost all performance features depend on topology and thread placement! (especially if SMT/Hyperthreading is on)

- Always observe the topology dependence of

- Intranode MPI performance

- OpenMP overheads

- Saturation effects / scalability behavior with bandwidth-bound code

- Enforce proper thread/process to core binding, using appropriate tools (whatever you use, but use SOMETHING)

- Learn how to take control of hybrid execution!

- Almost all performance features depend on topology and thread placement! (especially if SMT/Hyperthreading is on)

- Always observe the topology dependence of

- Intranode MPI performance

- OpenMP overheads

- Saturation effects / scalability behavior with bandwidth-bound code

- Enforce proper thread/process to core binding, using appropriate tools (whatever you use, but use SOMETHING)

- Memory page placement on ccNUMA nodes

- Automatic optimal page placement for one (or more) MPI processes per ccNUMA domain (solution A)

- Explicitly parallel first-touch initialization only required for multi-domain MPI processes (solution B)

# Programming models

- MPI + OpenMP

Hands-On #2

**Pinning**

General considerations

How to compile, link, and run

Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth Memory placement on ccNUMA systems

Topology and affinity on multicore

> Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

# Programming models - MPI + OpenMP

Case study:

The Multi-Zone

NAS Parallel Benchmarks

General considerations

How to compile, link, and run

Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth

Memory placement on ccNUMA systems Topology and affinity on multicore

Hands-on: Pinning

> Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

Communication overlap with OpenMP taskloops Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

## Load Balancing with hybrid programming

- On same or different level of parallelism

- OpenMP enables

- cheap dynamic and guided load-balancing

- via a parallelization option (clause on omp for / do directive)

- without additional software effort

- without explicit data movement

#### On MPI level

- Dynamic load balancing requires moving of parts of the data structure through the network

- Significant runtime overhead

- Complicated software → rarely implemented

#### MPI & OpenMP

Simple static load balancing on MPI level, \( \) medium-quality, dynamic or guided on OpenMP level

```

cheap implementation

```

```

#pragma omp parallel for schedule(dynamic)

for (i=0; i<n; i++) {

/* poorly balanced iterations */ ...

```

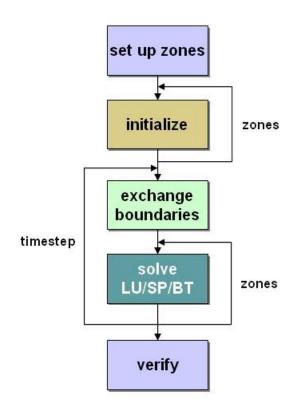

### The Multi-Zone NAS Parallel Benchmarks

|                        | MPI/<br>OpenMP | Seq           | Nested<br>OpenMP |

|------------------------|----------------|---------------|------------------|

| Time step              | sequential     | sequential    | sequential       |

| inter-zones            | MPI Processes  | direct access | OpenMP           |

| exchange<br>boundaries | Call MPI       | direct        | OpenMP           |

| intra-zones            | OpenMP         | sequential    | OpenMP           |

Multi-zone versions of the NAS Parallel Benchmarks LU,SP, and BT

- Two hybrid sample implementations

- Load balance heuristics part of sample codes

- https://www.nas.nasa.gov/publications/npb.html

## MPI/OpenMP BT-MZ structure

```

call omp set numthreads (weight)

subroutine zsolve (u, rsd,...)

do step = 1, itmax

call exch qbc(u, qbc, nx,...)

!$OMP PARALLEL

DEFAULT (SHARED)

call mpi_send/recv

!$OMP& PRIVATE(m,i,j,k...)

do k = 2, nz-1

!$OMP DO

do j = 2, ny-1

do zone = 1, num zones

do i = 2, nx-1

if (iam .eq. pzone id(zone)) then

do m = 1, 5

call zsolve(u,rsd,...) _

u(m,i,j,k) =

end if

dt*rsd(m,i,j,k-1)

end do

end do

end do

end do

end do

. . .

!$OMP END DO NOWAIT

end do

!SOMP END PARALLEL

```

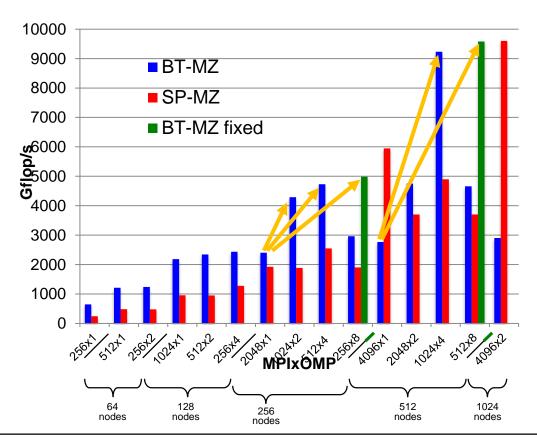

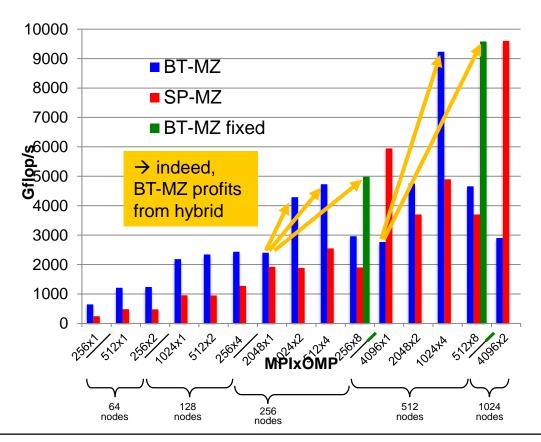

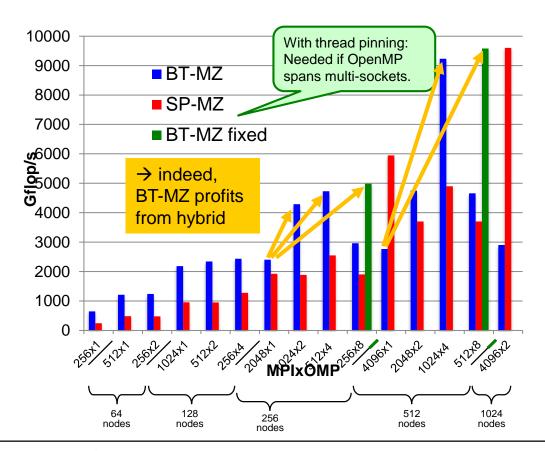

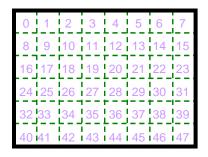

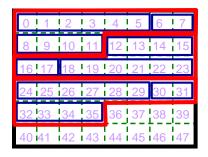

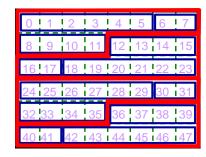

- Aggregate sizes:

- Class D: 1632 x 1216 x 34 grid points

- Class E: 4224 x 3456 x 92 grid points

- BT-MZ: (Block tridiagonal simulated CFD application)

- Alternative Directions Implicit (ADI) method

- #Zones: 1024 (D), 4096 (E)

- Size of the zones varies widely:

- large/small about 20

- requires multi-level parallelism to achieve a good load-balance

- SP-MZ: (Scalar Pentadiagonal simulated CFD application)

- #Zones: 1024 (D), 4096 (E)

- Size of zones identical

- no load-balancing required

- Aggregate sizes:

- Class D: 1632 x 1216 x 34 grid points

- Class E: 4224 x 3456 x 92 grid points

- BT-MZ: (Block tridiagonal simulated CFD application)

- Alternative Directions Implicit (ADI) method

- #Zones: 1024 (D), 4096 (E)

- Size of the zones varies widely:

- large/small about 20

- requires multi-level parallelism to achieve a good load-balance

- SP-MZ: (Scalar Pentadiagonal simulated CFD application)

- #Zones: 1024 (D), 4096 (E)

- Size of zones identical

- no load-balancing required

.

Expectations:

- Aggregate sizes:

- Class D: 1632 x 1216 x 34 grid points

- Class E: 4224 x 3456 x 92 grid points

- BT-MZ: (Block tridiagonal simulated CFD application)

- Alternative Directions Implicit (ADI) method

- #Zones: 1024 (D), 4096 (E)

- Size of the zones varies widely:

- large/small about 20

- requires multi-level parallelism to achieve a good load-balance

- SP-MZ: (Scalar Pentadiagonal simulated CFD application)

- #Zones: 1024 (D), 4096 (E)

- Size of zones identical

- no load-balancing required

#### Expectations:

Pure MPI: Loadbalancing problems!

Good candidate for MPI+OpenMP

- Aggregate sizes:

- Class D: 1632 x 1216 x 34 grid points

- Class E: 4224 x 3456 x 92 grid points

- BT-MZ: (Block tridiagonal simulated CFD application)

- Alternative Directions Implicit (ADI) method

- #Zones: 1024 (D), 4096 (E)

- Size of the zones varies widely:

- large/small about 20

- requires multi-level parallelism to achieve a good load-balance

- SP-MZ: (Scalar Pentadiagonal simulated CFD application)

- #Zones: 1024 (D), 4096 (E)

- Size of zones identical

- no load-balancing required

#### Expectations:

Pure MPI: Loadbalancing problems!

Good candidate for MPI+OpenMP

Load-balanced on MPI level: Pure MPI should perform best

# NPB-MZ Class E Scalability on Lonestar

# NPB-MZ Class E Scalability on Lonestar

#### NPB-MZ Class E Scalability on Lonestar

# Programming models

- MPI + OpenMP

Hands-On #3

Masteronly hybrid Jacobi

General considerations

How to compile, link, and run

Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth

Memory placement on ccNUMA systems

Topology and affinity on multicore

Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

> Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

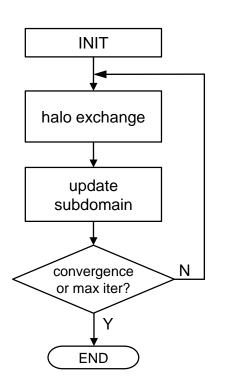

#### Example: MPI+OpenMP-Hybrid Jacobi solver

Source code: See <a href="http://tiny.cc/MPIX-VSC">http://tiny.cc/MPIX-VSC</a>

VSC LRZ

- This is a Jacobi solver (2D stencil code) with domain decomposition and halo exchange

- The given code is MPI-only. You can build it with make (take a look at the Makefile) and run it with something like this (adapt to local requirements):

```

$ <mpirun-or-whatever> -np <numprocs> ./jacobi.exe < input</pre>

```

Task: parallelize it with OpenMP to get a hybrid MPI+OpenMP code, and run it effectively on the given hardware.

#### Notes:

- The code is strongly memory bound at the problem size set in the input file

- Learn how to take control of affinity with MPI and especially with MPI+OpenMP

- Always run multiple times and observe performance variations

- If you know how, try to calculate the maximum possible performance and use it as a "light speed" baseline

http://tiny.cc/MPIX-VSC

http://tiny.cc/MPIX-LRZ alternative for the exercises

#### Example cont'd

- Tasks (we assume N<sub>c</sub> cores per CPU socket):

- Run the MPI-only code on one node with 1,...,N<sub>c</sub>,...,2\*N<sub>c</sub> processes (1 full node) and observe the achieved performance behavior

- Parallelize appropriate loops with OpenMP

- Run with OpenMP and 1 MPI process ("OpenMP-only") on 1,...,N<sub>c</sub>,...,2\*N<sub>c</sub> cores, compare with MPI-only run

- Run hybrid variants with different MPI vs. OpenMP ratios

- Things to observe

- Run-to-run performance variations

- Does the OpenMP/hybrid code perform as well as the MPI code? If it doesn't, fix it!

http://tiny.cc/MPIX-VSC

http://tiny.cc/MPIX-LRZ alternative for the exercises

see also login-slides

# Programming models

- MPI + OpenMP

# Overlapping Communication and Computation

General considerations

How to compile, link, and run

Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth

Memory placement on ccNUMA systems

Topology and affinity on multicore

Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

> Overlapping communication and computation

Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

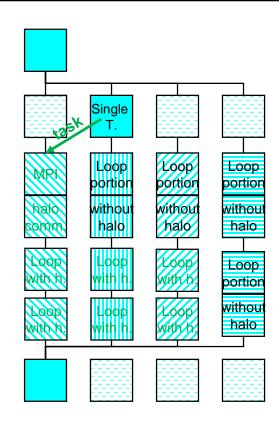

```

for (iteration ....)

{

#pragma omp parallel

numerical code

/* end parallel */

/* on master only */

MPI_Send(halos);

MPI_Recv(halos);

} /*end for loop*/

```

```

for (iteration ....)

{

#pragma omp parallel

numerical code

/* end parallel */

/* on master only */

MPI_Send(halos);

MPI_Recv(halos);

} /*end for loop*/

```

```

for (iteration ....)

{

#pragma omp parallel

numerical code

/* end parallel */

/* on master only */

MPI_Send(halos);

MPI_Recv(halos);

} /*end for loop*/

```

```

for (iteration ....)

{

#pragma omp parallel

numerical code

/* end parallel */

/* on master only */

MPI_Send(halos);

MPI_Recv(halos);

} /*end for loop*/

```

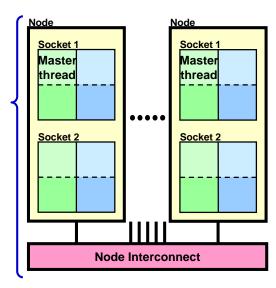

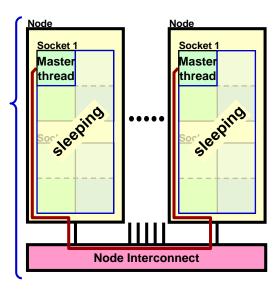

#### Problem:

Sleeping threads are wasting CPU time

```

for (iteration ....)

{

#pragma omp parallel

numerical code

/* end parallel */

/* on master only */

MPI_Send(halos);

MPI_Recv(halos);

} /*end for loop*/

```

#### Problem:

- Sleeping threads are wasting CPU time

- Solution:

- Overlapping of computation and communication

г

```

for (iteration ....)

{

#pragma omp parallel

numerical code

/* end parallel */

/* on master only */

MPI_Send(halos);

MPI_Recv(halos);

} /*end for loop*/

```

#### Problem:

Sleeping threads are wasting CPU time

#### Solution:

- Overlapping of computation and communication

- Limited benefit:

- Best case: reduces communication overhead from 50% to 0%

- $\rightarrow$  speedup of 2x

- Usual case of 20% to 0%

- $\rightarrow$  speedup of 1.25x

- Requires significant work → later

#### Nonblocking vs. threading for overlapped comm.

- Why not use nonblocking calls?

- Asynchronous progress not guaranteed

- Options (implementation dependent):

- Communication offload to NIC

- Additional internal progress thread (MPI\_ASYNC... with MPICH)

- Intranode and internode communication may be handled very differently

- Using threading for communication overlap

- One or more threads/tasks handles communication, rest of team "do the work"

- How to organize the work sharing among all threads?

- Non-communicating threads

- Communicating threads after communication is over

- Not all of the work can usually be overlapped → see next slide

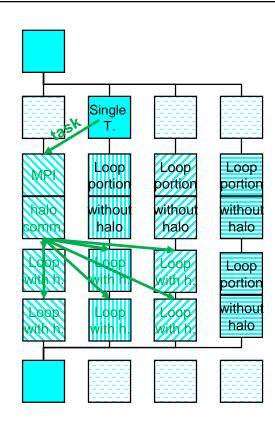

#### Using threading/tasking for comm. overlap

#### Using threading/tasking for comm. overlap

#### Explicit overlapping of communication and computation

#### The basic principle appears simple:

```

#pragma omp parallel

// ... do other parallel work

if (thread ID < 1) {

MPI Send/Recv ... // comm. halo data

} else {

// Work on data that is independent

// of halo data

} // end omp parallel

// Now work on data that needs the

// halo data (all threads)

```

#### Explicit overlapping of communication and computation

#### The basic principle appears simple:

```

#pragma omp parallel

// ... do other parallel work

if (thread ID < 1) {

MPI Send/Recv ... // comm. halo data

} else {

// Work on data that is independent

// of halo data

} // end omp parallel

// Now work on data that needs the

// halo data (all threads)

```

#### Explicit overlapping of communication and computation

The basic principle appears simple:

```

#pragma omp parallel

// ... do other parallel work

if (thread ID < 1) {

MPI Send/Recv ... // comm. halo data

} else {

// Work on data that is independent

// of halo data

} // end omp parallel

// Now work on data that needs the

// halo data (all threads)

```

#### Overlapping communication with computation

#### Three problems:

- Application problem: separate application into

- code that can run before the halo data is received

- code that needs halo data

- May be hard to do

- Thread-rank problem: distinguish comm. / comp. via thread ID

- Work sharing and load balancing is harder

- Options

- Fully manual work distribution

- Nested parallelism

- Tasking & taskloops

- Partitioned comm (MPI-4.0)

- Optimal memory placement on ccNUMA may be difficult

#### Overlapping communication with computation

#### Three problems:

- Application problem: separate application into

- code that can run before the halo data is received

- code that needs halo data

- May be hard to do

- Thread-rank problem: distinguish comm. / comp. via thread ID

- Work sharing and load balancing is harder

- Options

- Fully manual work distribution

- Nested parallelism

- Tasking & taskloops

- Partitioned comm (MPI-4.0)

- Optimal memory placement on ccNUMA may be difficult

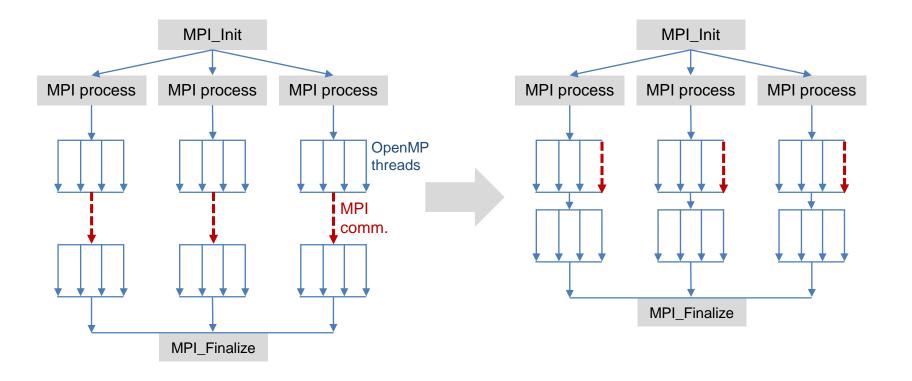

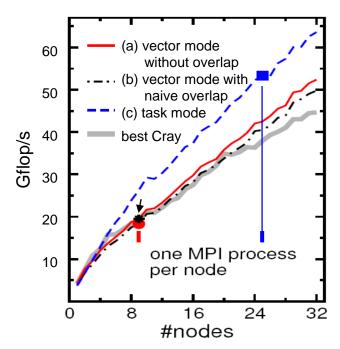

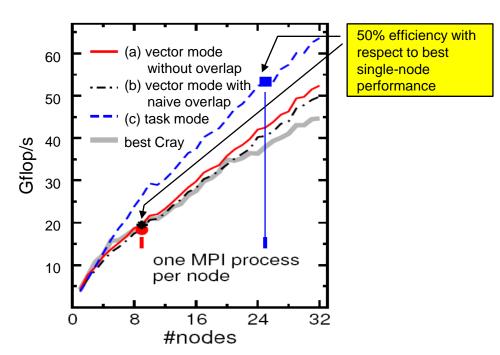

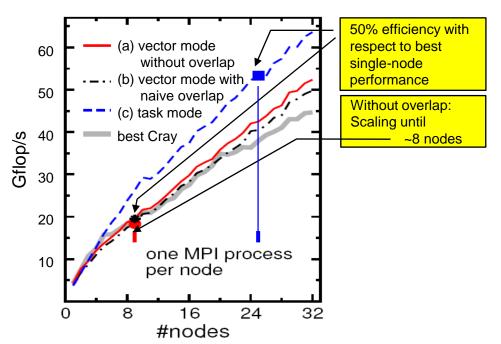

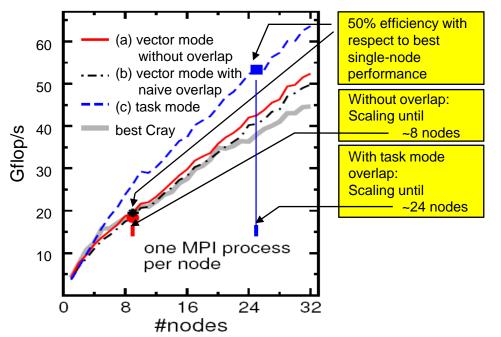

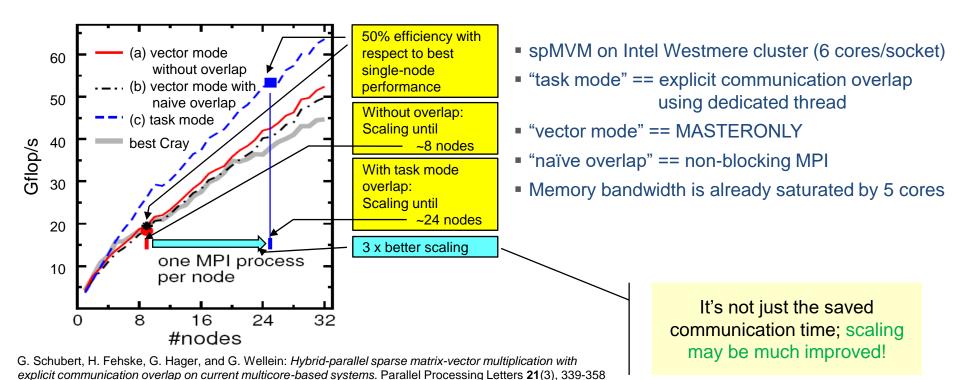

- spMVM on Intel Westmere cluster (6 cores/socket)

- "task mode" == explicit communication overlap using dedicated thread

- "vector mode" == MASTERONLY

- "naïve overlap" == non-blocking MPI

- Memory bandwidth is already saturated by 5 cores

G. Schubert, H. Fehske, G. Hager, and G. Wellein: *Hybrid-parallel sparse matrix-vector multiplication with explicit communication overlap on current multicore-based systems.* Parallel Processing Letters **21**(3), 339-358 (2011). DOI: 10.1142/S0129626411000254

- spMVM on Intel Westmere cluster (6 cores/socket)

- "task mode" == explicit communication overlap using dedicated thread

- "vector mode" == MASTERONLY

- "naïve overlap" == non-blocking MPI

- Memory bandwidth is already saturated by 5 cores

G. Schubert, H. Fehske, G. Hager, and G. Wellein: *Hybrid-parallel sparse matrix-vector multiplication with explicit communication overlap on current multicore-based systems.* Parallel Processing Letters **21**(3), 339-358 (2011). DOI: 10.1142/S0129626411000254

- spMVM on Intel Westmere cluster (6 cores/socket)

- "task mode" == explicit communication overlap using dedicated thread

- "vector mode" == MASTERONLY

- "naïve overlap" == non-blocking MPI

- Memory bandwidth is already saturated by 5 cores

G. Schubert, H. Fehske, G. Hager, and G. Wellein: *Hybrid-parallel sparse matrix-vector multiplication with explicit communication overlap on current multicore-based systems.* Parallel Processing Letters **21**(3), 339-358 (2011). DOI: 10.1142/S0129626411000254

- spMVM on Intel Westmere cluster (6 cores/socket)

- "task mode" == explicit communication overlap using dedicated thread

- "vector mode" == MASTERONLY

- "naïve overlap" == non-blocking MPI

- Memory bandwidth is already saturated by 5 cores

G. Schubert, H. Fehske, G. Hager, and G. Wellein: *Hybrid-parallel sparse matrix-vector multiplication with explicit communication overlap on current multicore-based systems*. Parallel Processing Letters **21**(3), 339-358 (2011). DOI: 10.1142/S0129626411000254

Rolf Rabenseifner (HLRS), Georg Hager (NHR@FAU), Claudia Blaas-Schenner (VSC, TU Wien)

(2011). DOI: 10.1142/S0129626411000254

# Programming models - MPI + OpenMP

# Communication overlap with OpenMP taskloops

General considerations

How to compile, link, and run

Hands-on: Hello hybrid!

System topology, ccNUMA, and memory bandwidth Memory placement on ccNUMA systems

Topology and affinity on multicore

Hands-on: Pinning

Case study: The Multi-Zone NAS Parallel Benchmarks

Hands-on: Masteronly hybrid Jacobi

Overlapping communication and computation

> Communication overlap with OpenMP taskloops

Hands-on: Taskloop-based hybrid Jacobi

Main advantages, disadvantages, conclusions

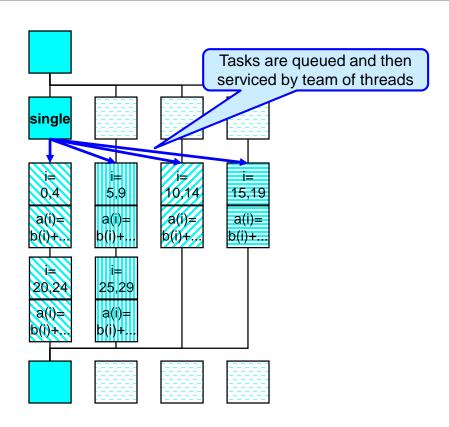

- Immediately following loop executed in several tasks

- Not a work-sharing directive!

- Should be executed only by one thread!

- Immediately following loop executed in several tasks

- Not a work-sharing directive!

- Should be executed only by one thread!

A task can be run by any thread, across NUMA nodes

→ <sup>(2)</sup> perfect first touch impossible!

- Immediately following loop executed in several tasks

- Not a work-sharing directive!

- Should be executed only by one thread!

A task can be run by any thread, across NUMA nodes

→ ② perfect first touch impossible!

```

Fortran:

```

```

!$OMP taskloop [clause[[,]clause]...]

do_loop

[!$OMP end taskloop [nowait]]

```

• If used, the end do directive must appear immediately after the end of the loop

- Immediately following loop executed in several tasks

- Not a work-sharing directive!

- Should be executed only by one thread!

A task can be run by any thread, across NUMA nodes

→ ② perfect first touch impossible!

Fortran:

```

!$OMP taskloop [clause[[,]clause]...]

do_loop

[!$OMP end taskloop [nowait]]

```

Loop iterations must be independent, i.e., they can be executed in parallel

• If used, the end do directive must appear immediately after the end of the loop

- Immediately following loop executed in several tasks

- Not a work-sharing directive!

- Should be executed only by one thread!

A task can be run by any thread, across NUMA nodes

→ ② perfect first touch impossible!

Fortran:

```

!$OMP taskloop [clause[[,]clause]...]

do_loop

[!$OMP end taskloop [nowait]]

Loop iterations must be independent, i.e., they can be executed in parallel

```

• If used, the end do directive must appear immediately after the end of the loop

- " C/C++:

#pragma omp taskloop [ clause [ [ , ] clause ] ... ] new-line

for-loop

- The corresponding for-loop must have canonical shape → next slide

#### OpenMP taskloop Directive - Details

```

clause can be one of the following:

• if([taskloop:]scalar-expr)

[a task clause]

shared (list)

[a task clause]

private (list), firstprivate (list)

[a do/for clause] [a task clause]

lastprivate(list)

[a do/for clause]

default(shared | none | ...)

[a task clause]

collapse(n)

[a do/for clause]

grainsize(grain-size)

num tasks(num-tasks)

untied, mergeable

[a task clause]

final(scalar-expr), priority(priority-value)

[a task clause]

nogroup

reduction (operator:list)

[a do/for clause]

do/ for clauses that are not valid on a taskloop:

schedule(type[, chunk]), nowait

• linear(list[: linear-step]), ordered [(n)]

```

#### OpenMP taskloop Directive - Details

```

clause can be one of the following:

• if([taskloop:]scalar-expr)

[a task clause]

shared (list)

[a task clause]

private (list), firstprivate (list)

[a do/for clause] [a task clause]

lastprivate(list)

[a do/for clause]

default(shared | none | ...)

[a task clause]

collapse(n)

[a do/for clause]

exclusive

num tasks(num-tasks)

untied, mergeable

[a task clause]

final(scalar-expr), priority(priority-value)

[a task clause]

nogroup

reduction (operator:list)

[a do/for clause]

do/ for clauses that are not valid on a taskloop:

schedule(type[, chunk]), nowait

linear(list[: linear-step]), ordered [(n)]

```

#### OpenMP taskloop Directive - Details

```

clause can be one of the following:

• if([taskloop:]scalar-expr)

[a task clause]

shared (list)

[a task clause]

private (list), firstprivate (list)

[a do/for clause] [a task clause]

lastprivate(list)

[a do/for clause]

default(shared | none | ...)

[a task clause]

collapse(n)

[a do/for clause]

exclusive

num tasks(num-tasks)

untied, mergeable

[a task clause]

final(scalar-expr), priority(priority-value)

[a task clause]

nogroup

Since

OpenMP 5.0!

■ reduction (operator:list) ←

[a do/for clause]

do/ for clauses that are not valid on a taskloop:

schedule(type[, chunk]), nowait

linear(list[: linear-step]), ordered [(n)]

```

#### OpenMP single & taskloop Directives

```

C/C++

```

```

C / C++:

```

```

#pragma omp parallel

{

#pragma omp single

{

A lot more tasks

than threads may be produced to achieve a good load balancing

}

/*omp end single*/

} /*omp end parallel*/

```

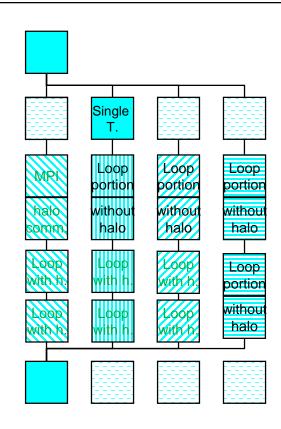

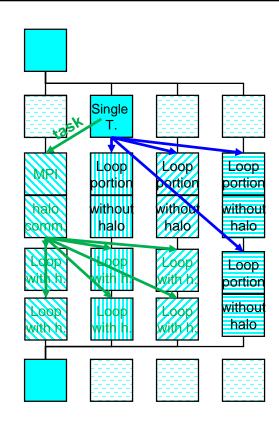

#### Comm. overlap with task & taskloop Directives - C/C++

```

Introduction to OpenMP

C/C++

#pragma omp parallel

#pragma omp single

#pragma omp task

// MPI halo communication:

MPI Send/Recv...

// numerical loop using halo data:

Number of

#pragma omp taskloop

tasks may

for (i=0; i<100; i++)

be

Extensions in OpenMP-4.0 and

a[i] = b[i] + b[i-1] + b[i+1] + b[i-2]...;

influenced

} /*omp end of halo task */

with

grainsize or

num tasks

numerical loop without halo data:

clauses

#pragma omp taskloop

for (i=100; i<10000; i++)

a[i] = b[i] + b[i-1] + b[i+1] + b[i-2]...;

} /*omp end single */

} /*omp end parallel*/

4.5

```

[07]

#### Comm. overlap with task & taskloop Directives - C/C++

```

Introduction to OpenMP

C/C++

#pragma omp parallel

#pragma omp single

#pragma omp task

// MPI halo communication:

MPI Send/Recv...

// numerical loop using halo data:

Number of

#pragma omp taskloop

tasks may

for (i=0; i<100; i++)

be

Extensions in OpenMP-4.0 and

a[i] = b[i] + b[i-1] + b[i+1] + b[i-2]...;

influenced

} /*omp end of halo task */

with

grainsize or

num tasks

numerical loop without halo data:

clauses

#pragma omp taskloop

for (i=100; i<10000; i++)

a[i] = b[i] + b[i-1] + b[i+1] + b[i-2]...;

} /*omp end single */

} /*omp end parallel*/

4.5

```

[07]

#### Comm. overlap with task & taskloop Directives - C/C++

```

Introduction to OpenMP

C/C++

#pragma omp parallel

#pragma omp single

#pragma omp task

// MPI halo communication:

MPI Send/Recv...

// numerical loop using halo data:

Number of

#pragma omp taskloop

tasks may

for (i=0; i<100; i++)

be

Extensions in OpenMP-4.0 and

a[i] = b[i] + b[i-1] + b[i+1] + b[i-2]...;

influenced

} /*omp end of halo task */

with

grainsize or

num tasks

numerical loop without halo data:

clauses

#pragma omp taskloop

for (i=100; i<10000; i++)

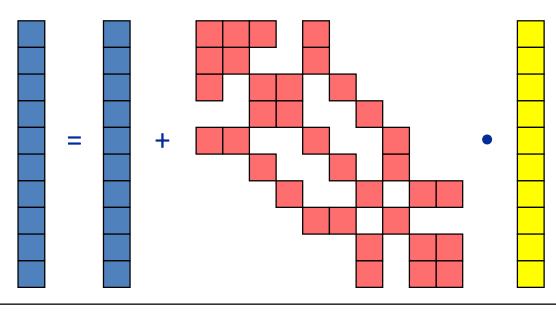

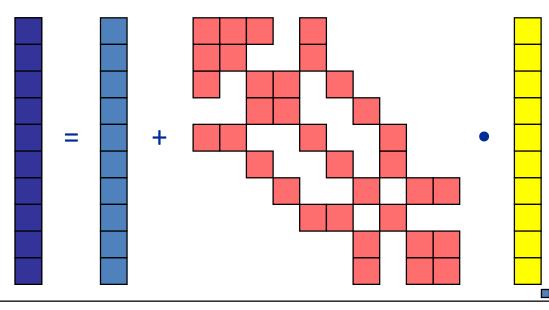

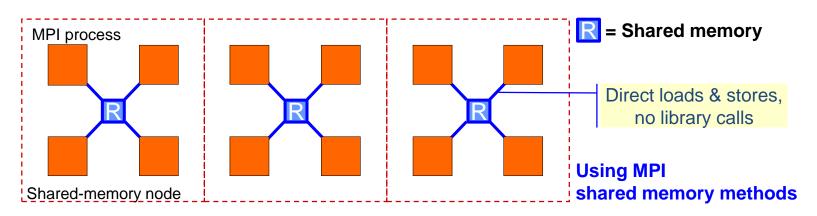

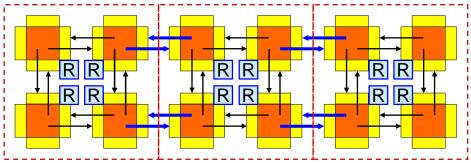

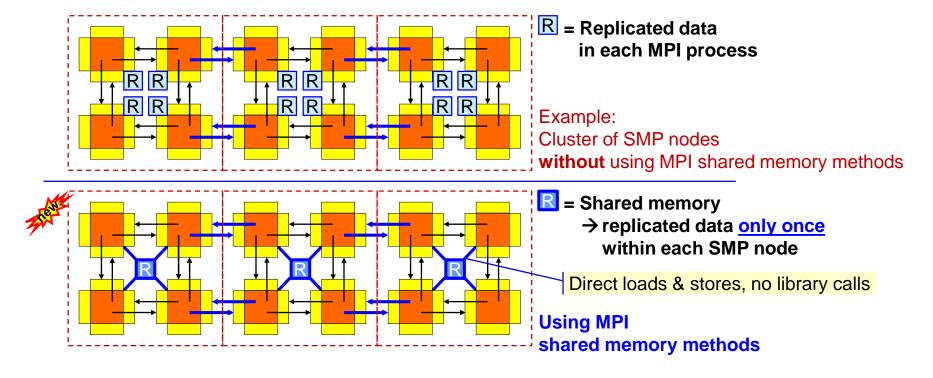

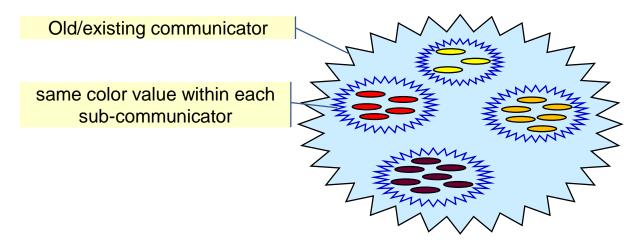

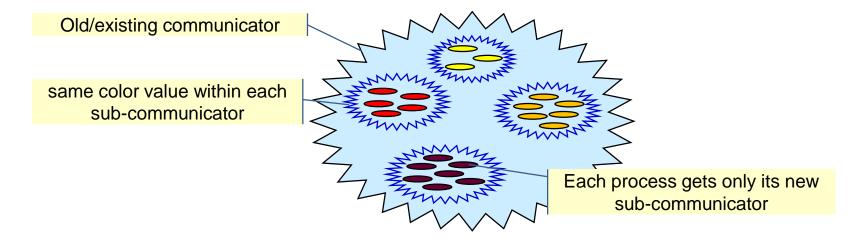

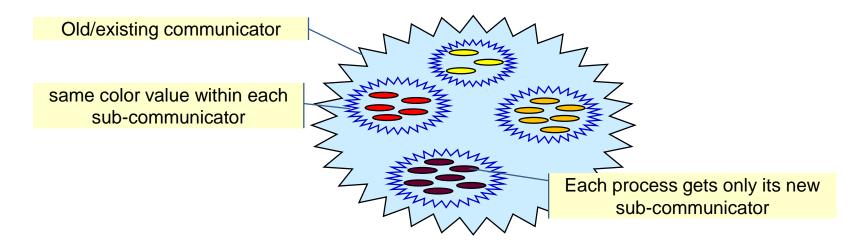

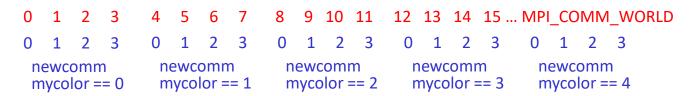

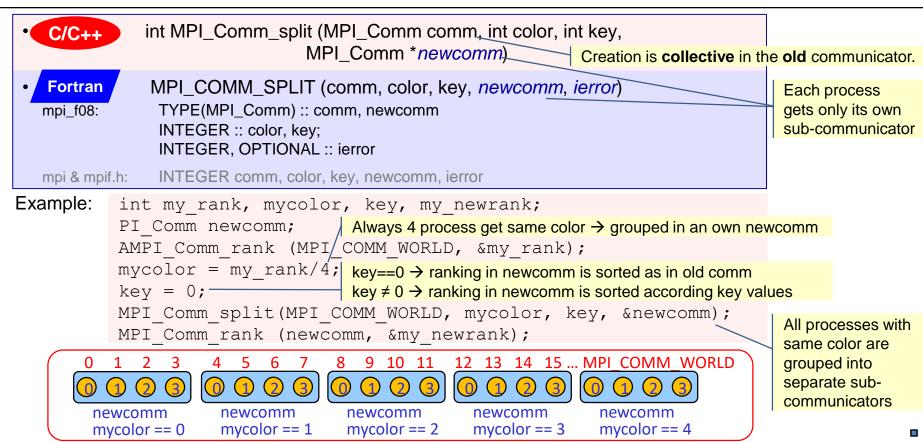

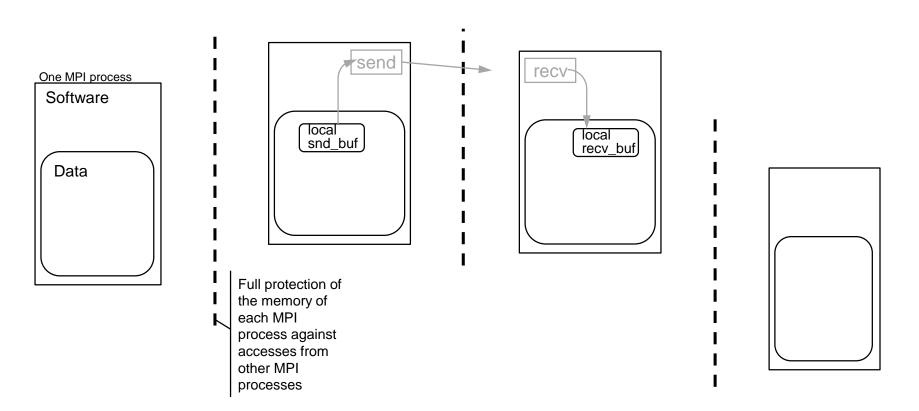

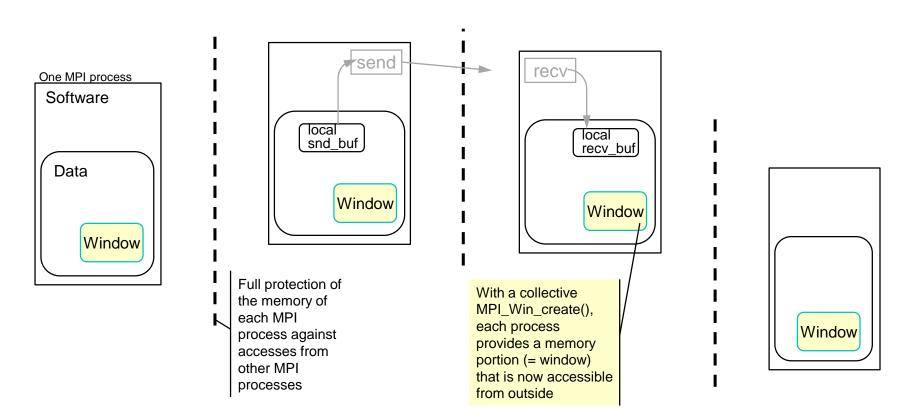

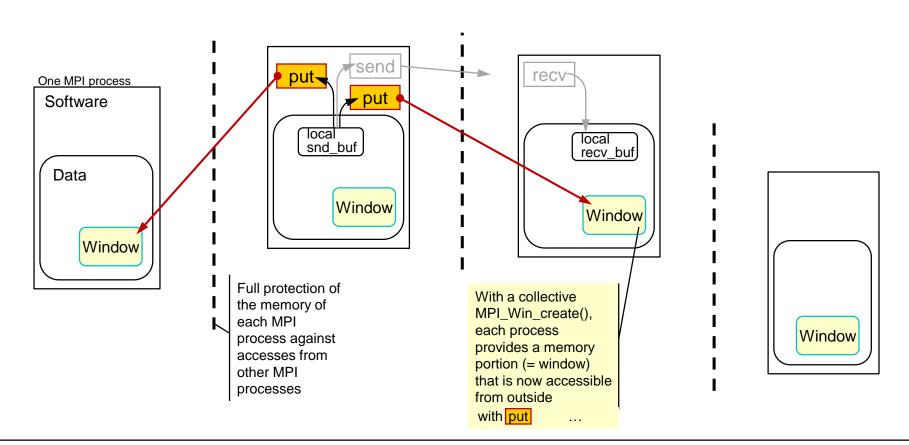

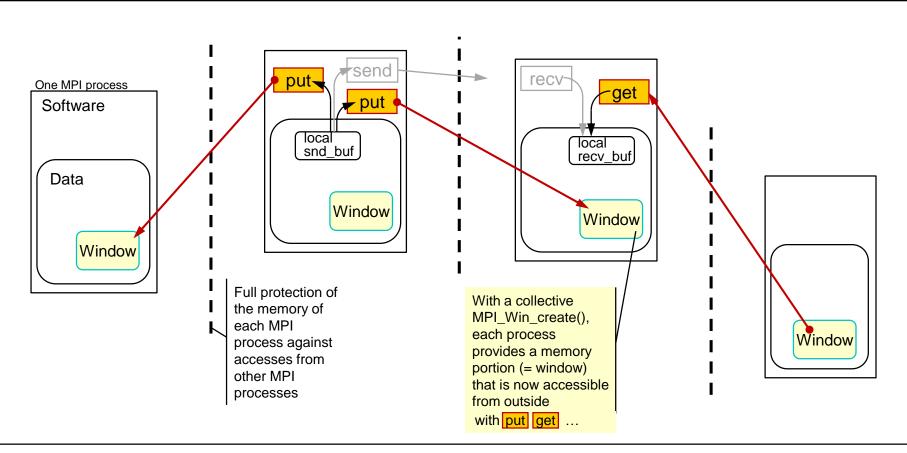

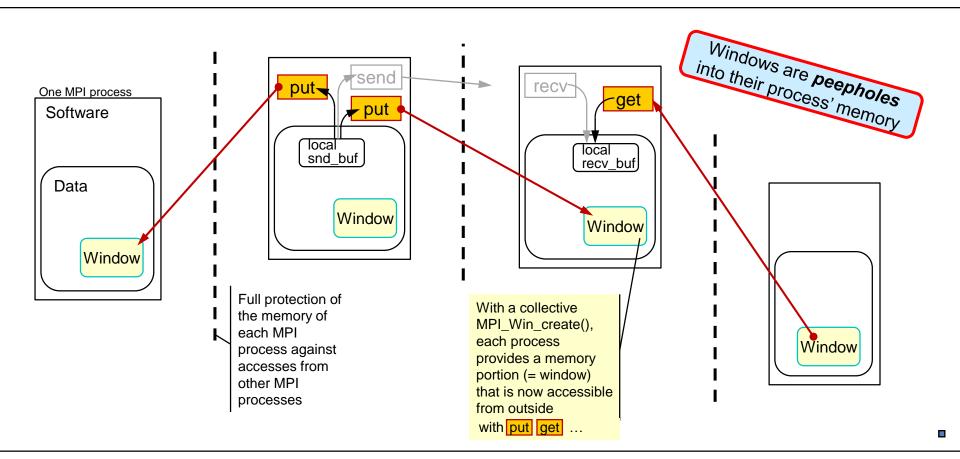

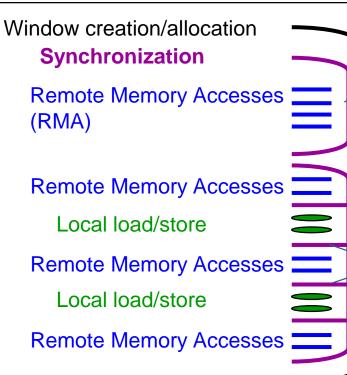

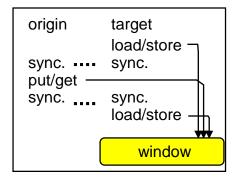

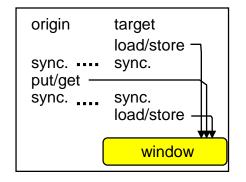

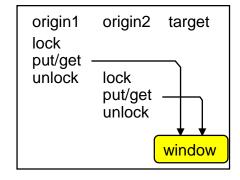

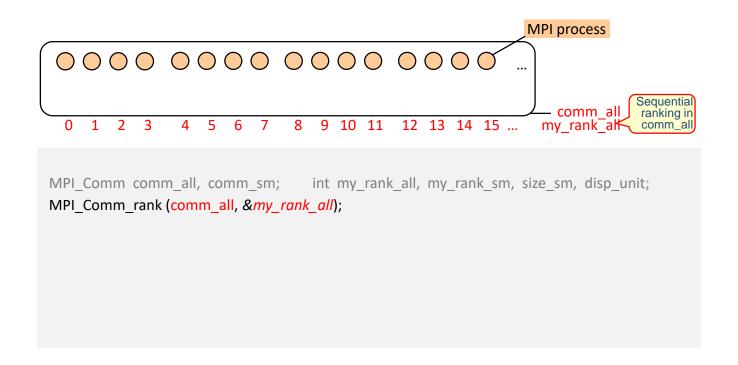

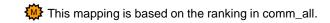

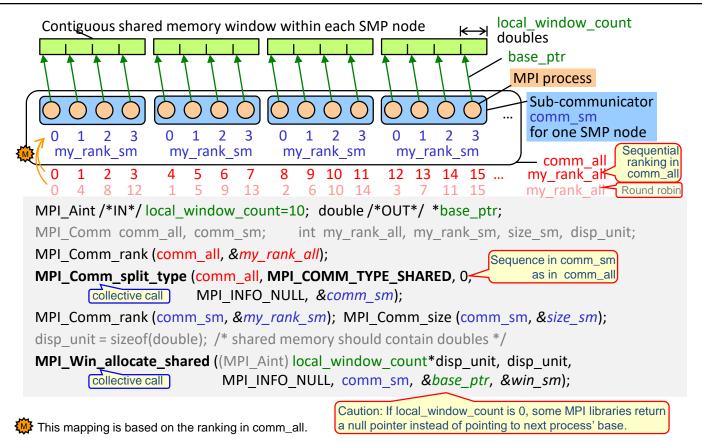

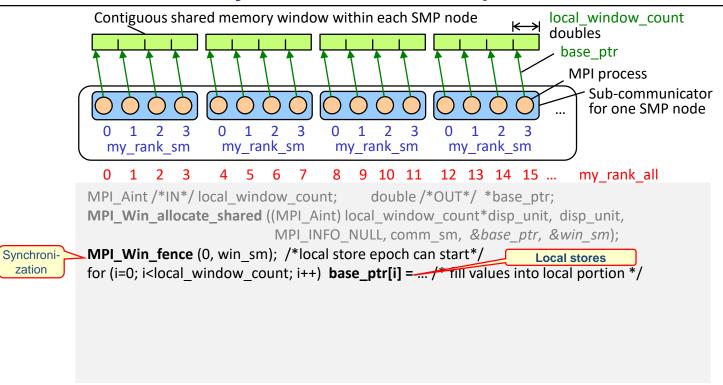

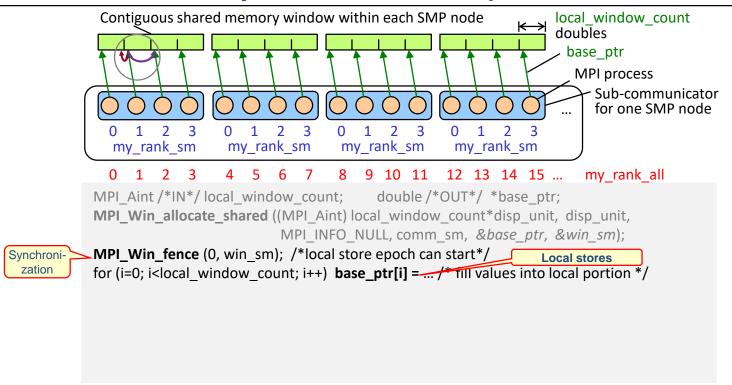

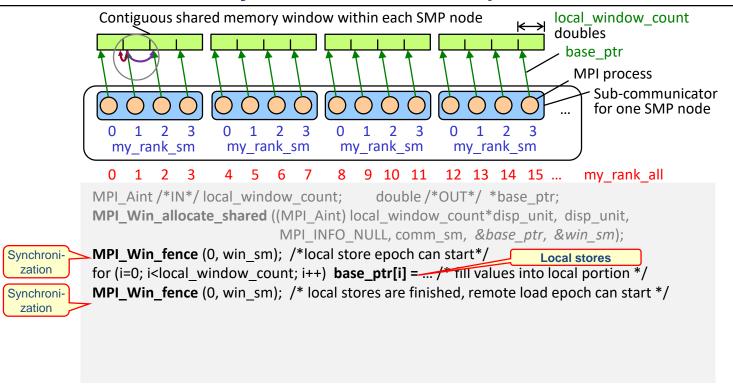

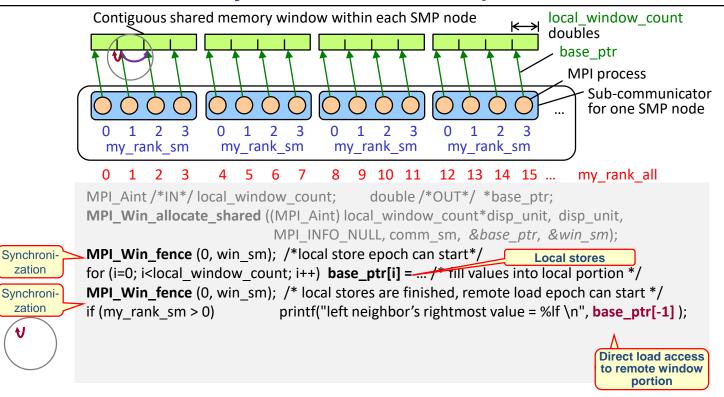

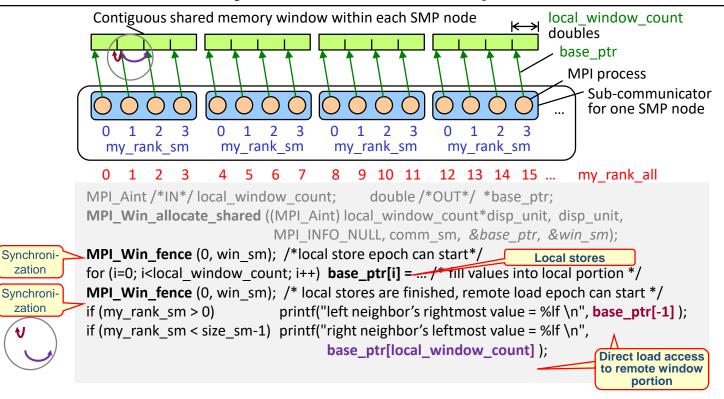

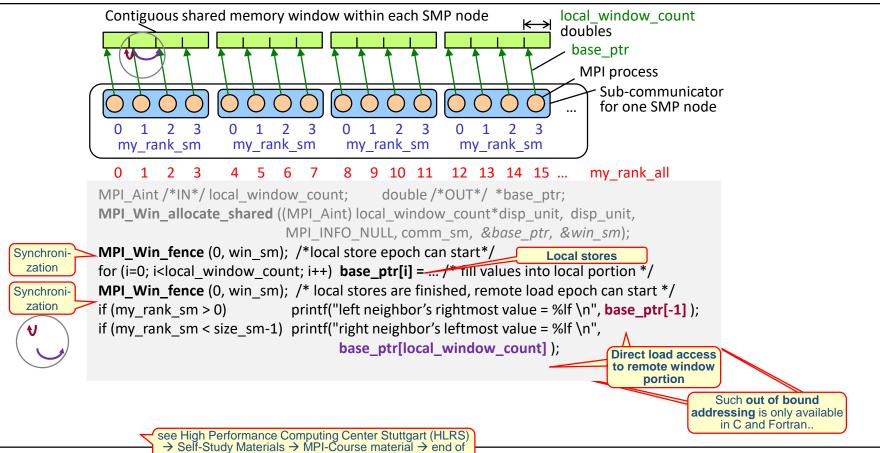

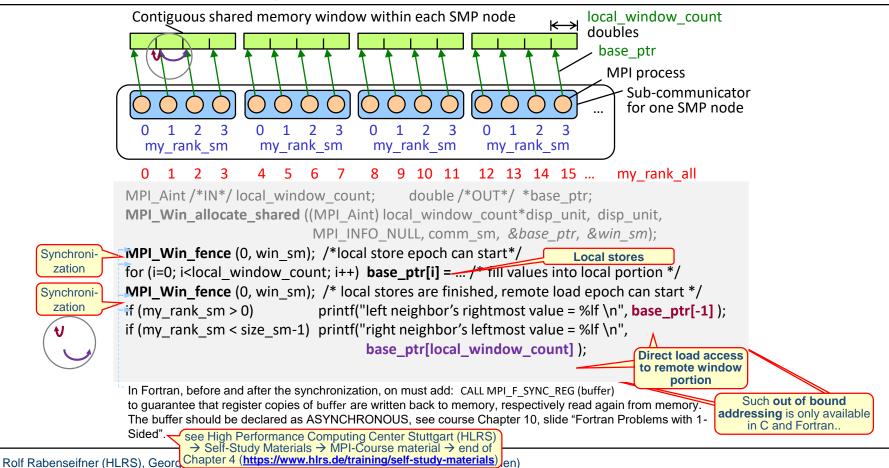

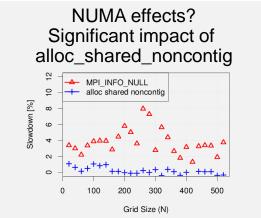

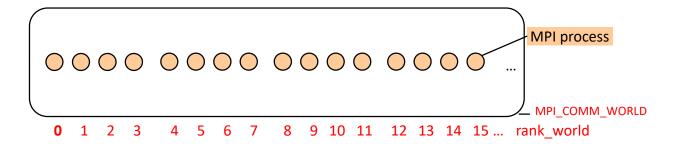

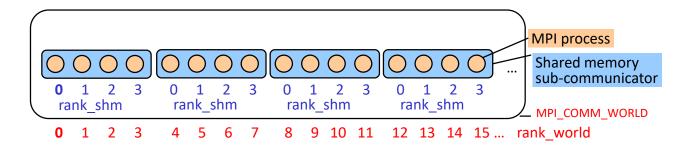

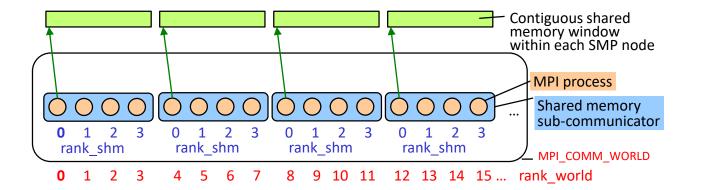

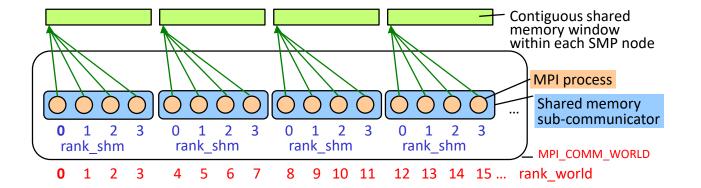

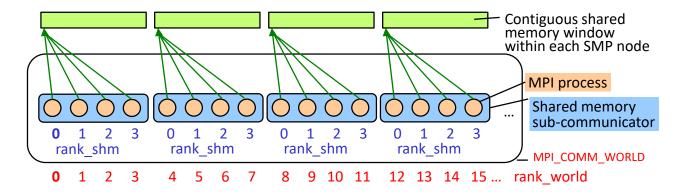

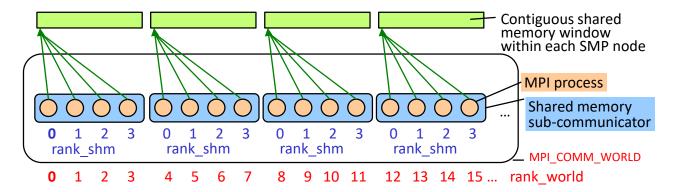

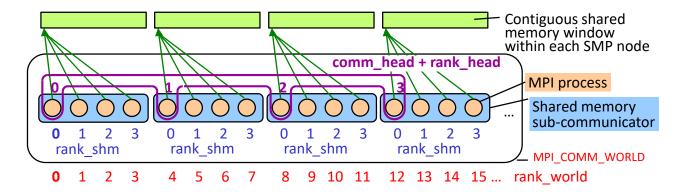

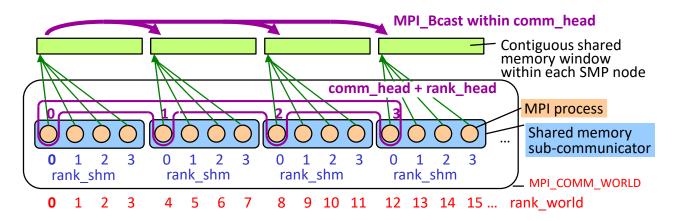

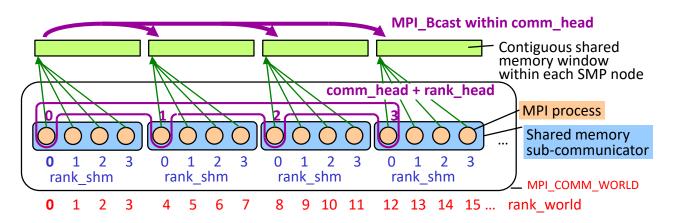

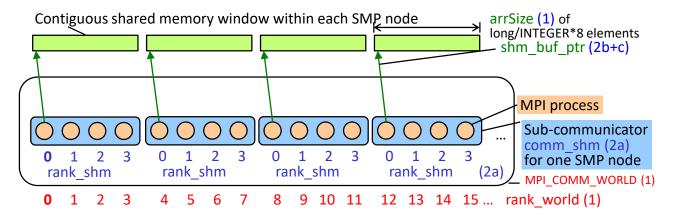

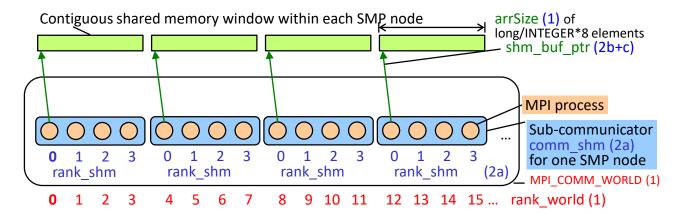

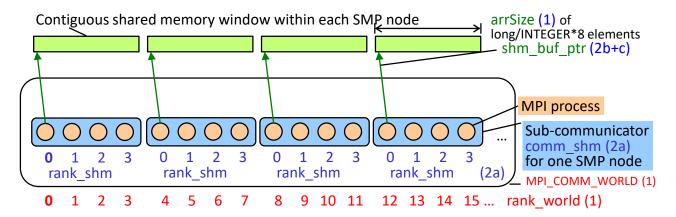

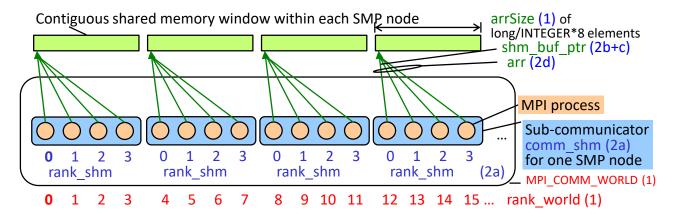

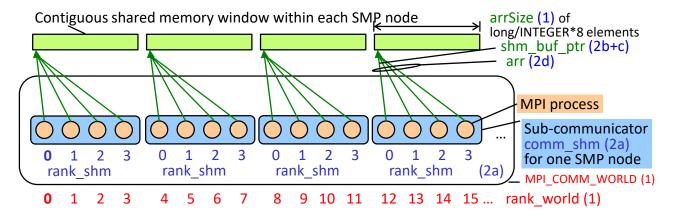

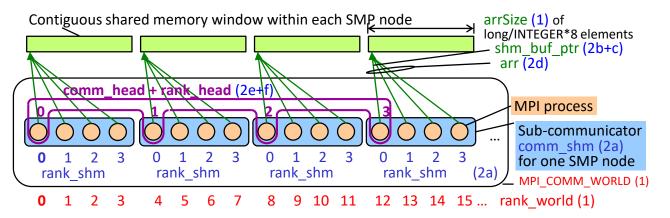

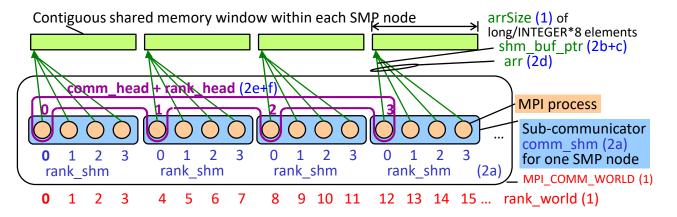

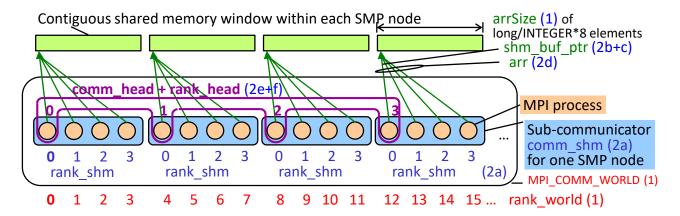

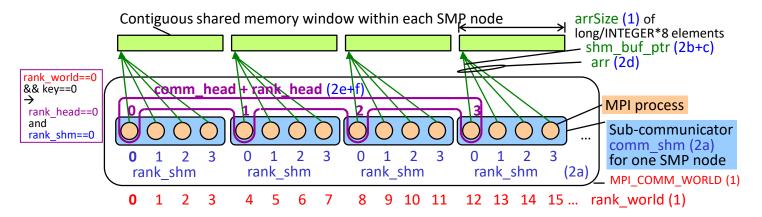

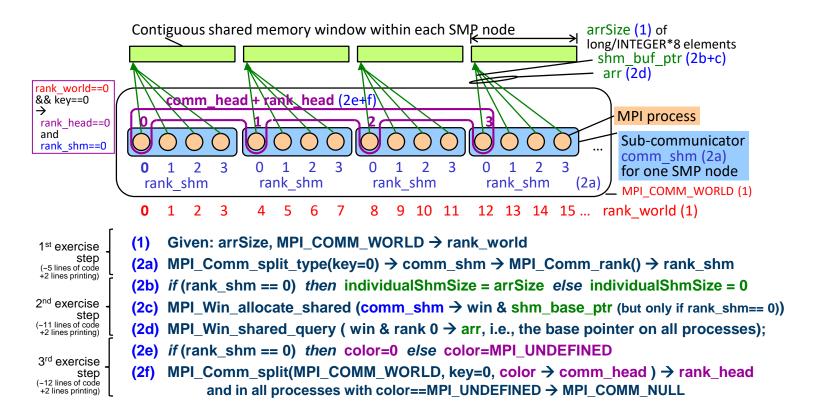

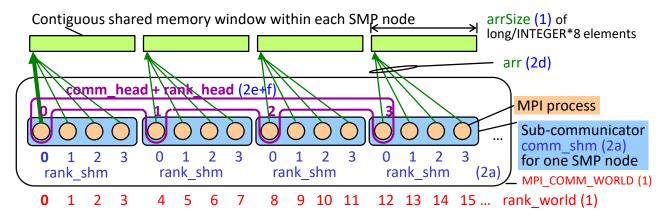

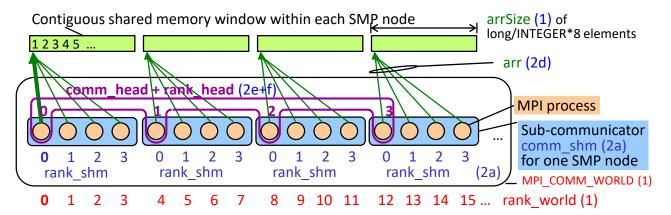

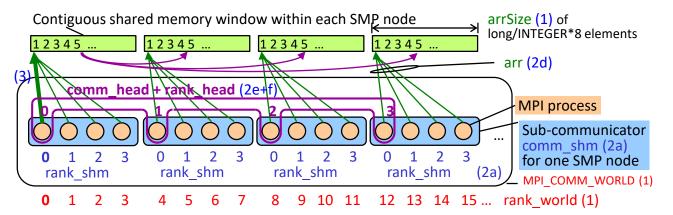

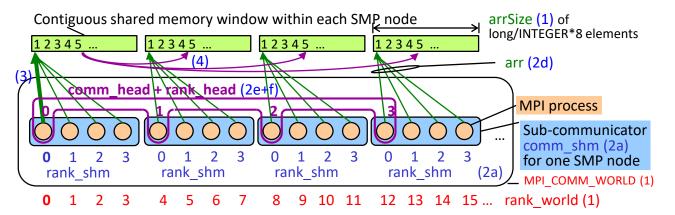

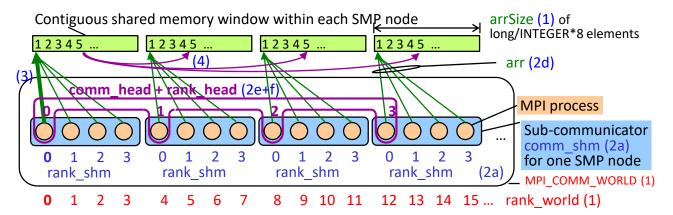

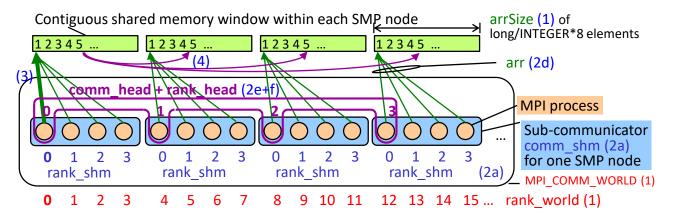

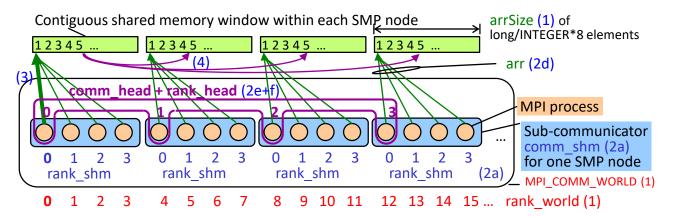

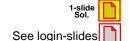

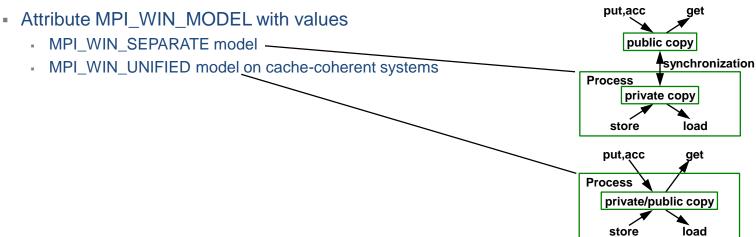

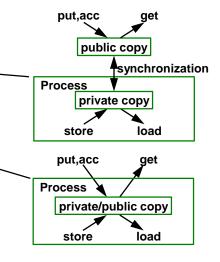

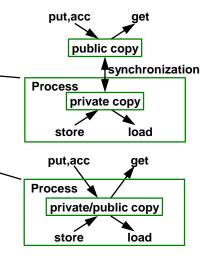

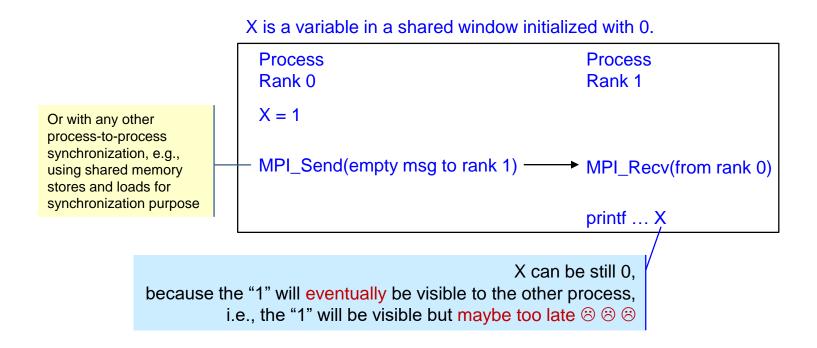

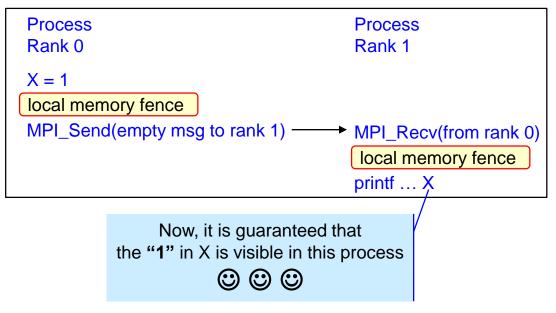

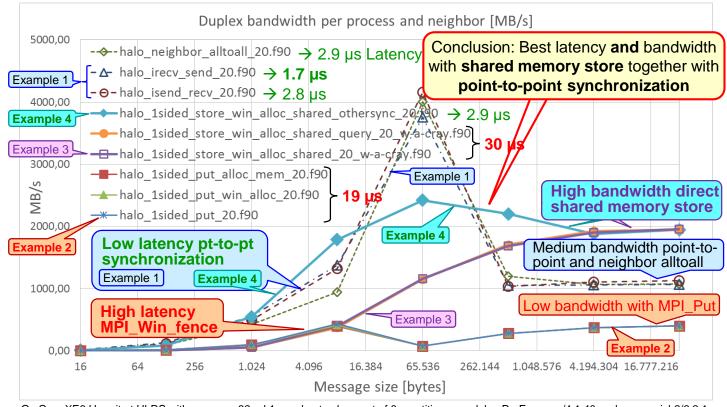

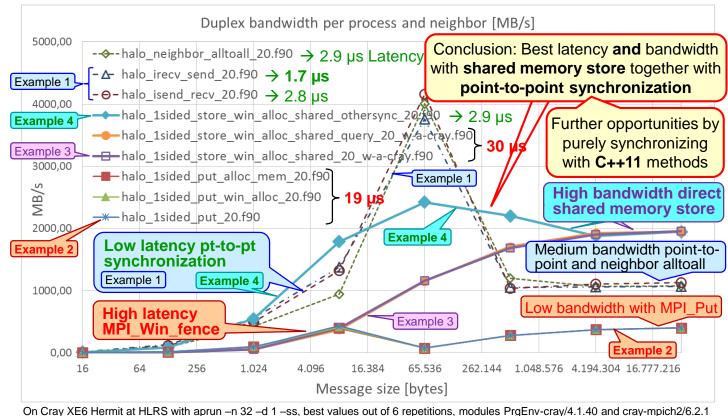

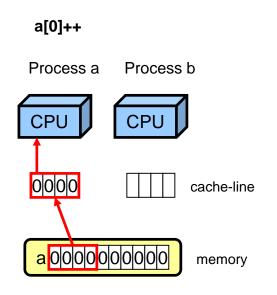

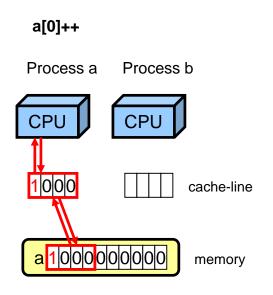

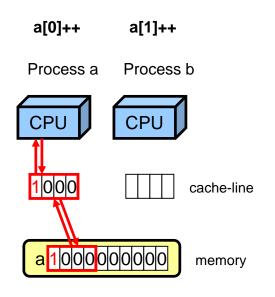

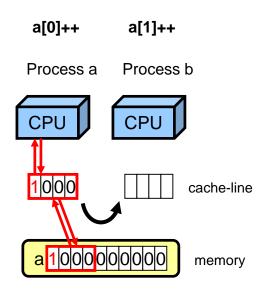

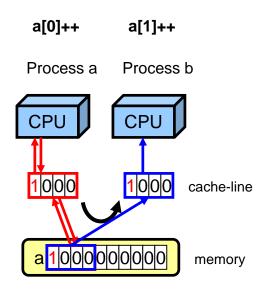

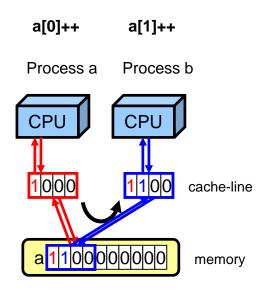

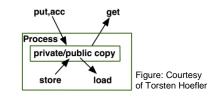

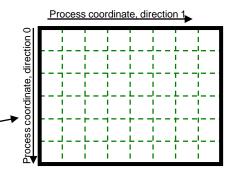

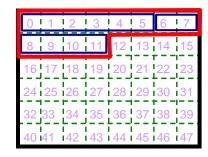

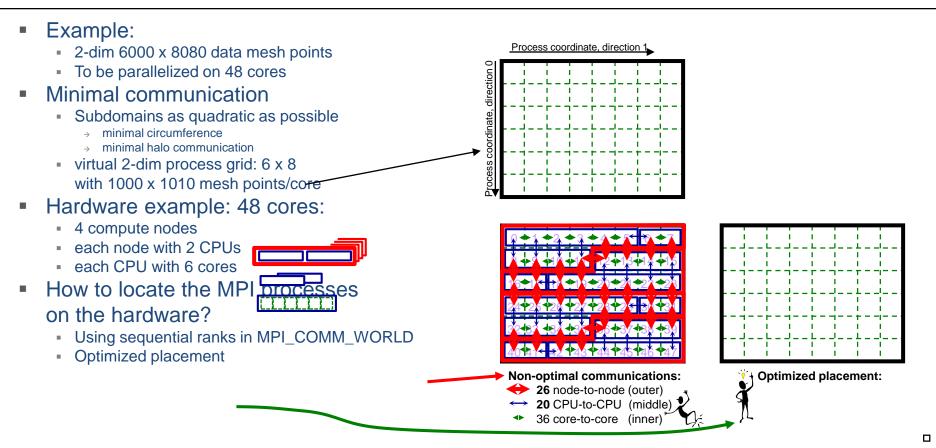

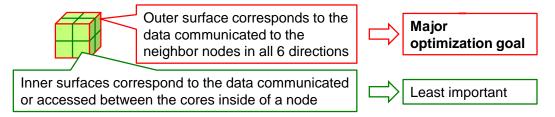

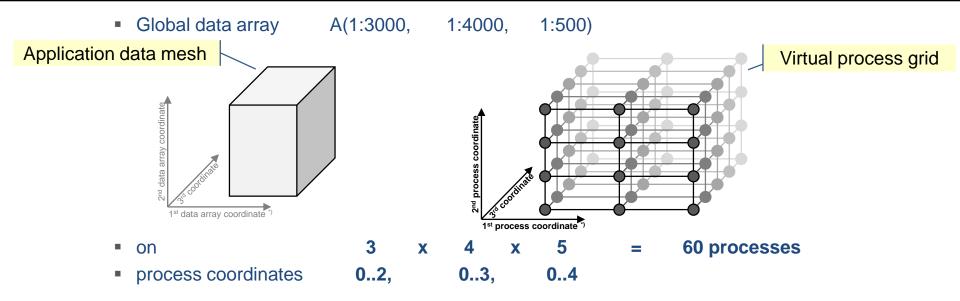

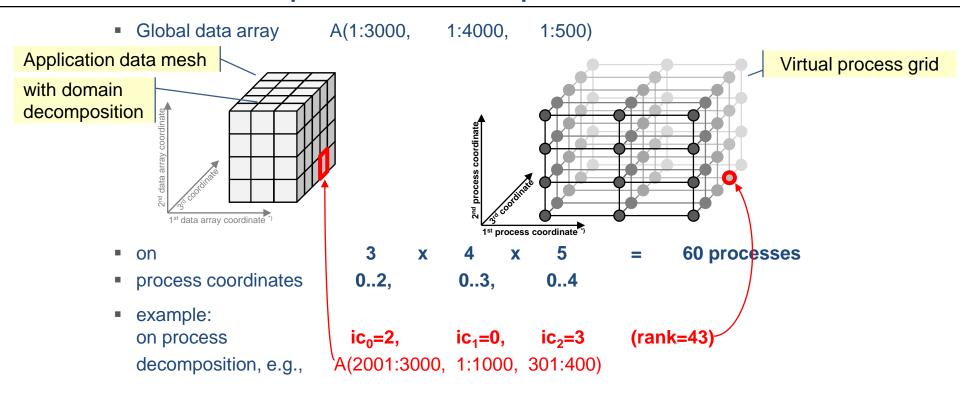

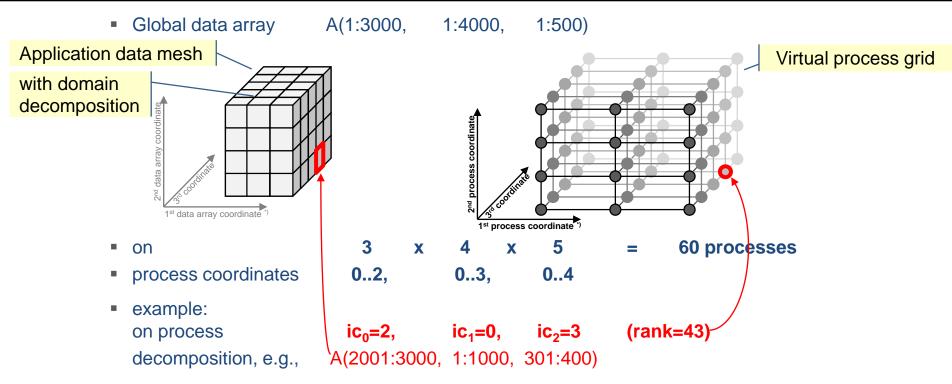

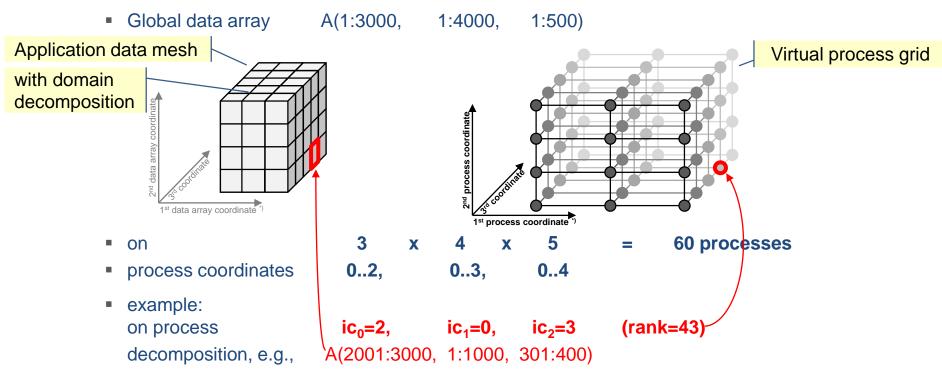

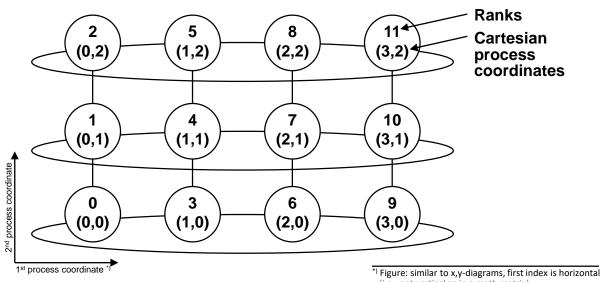

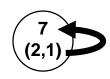

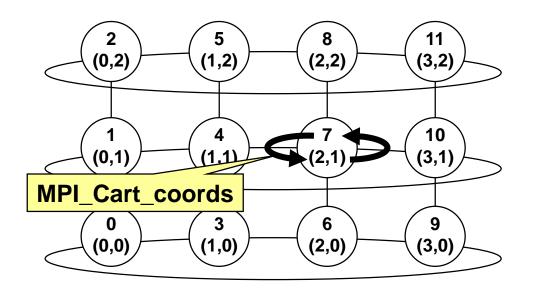

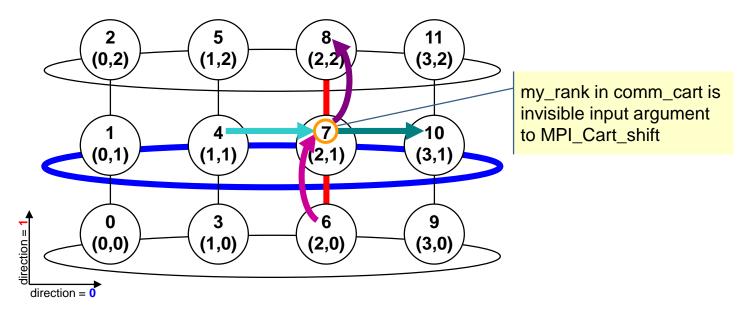

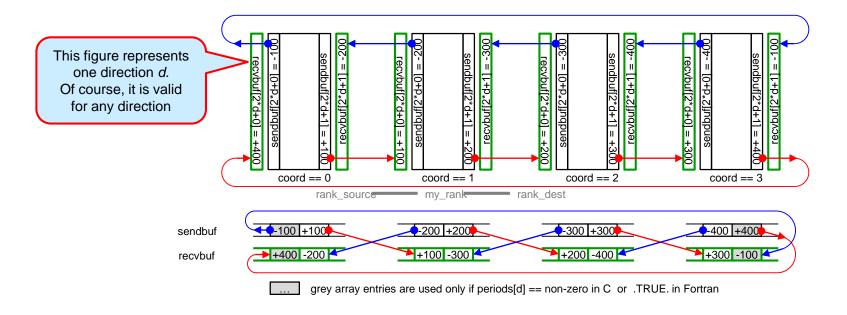

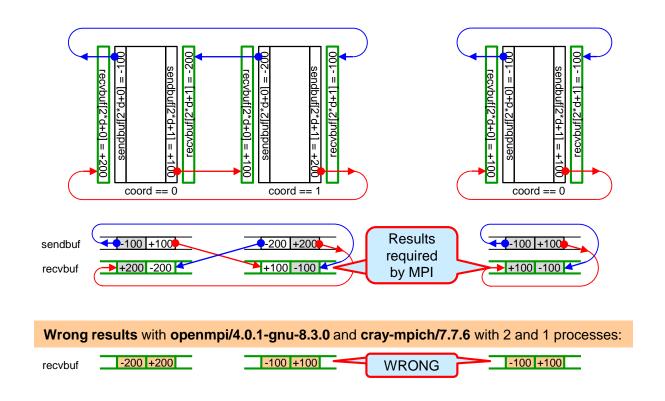

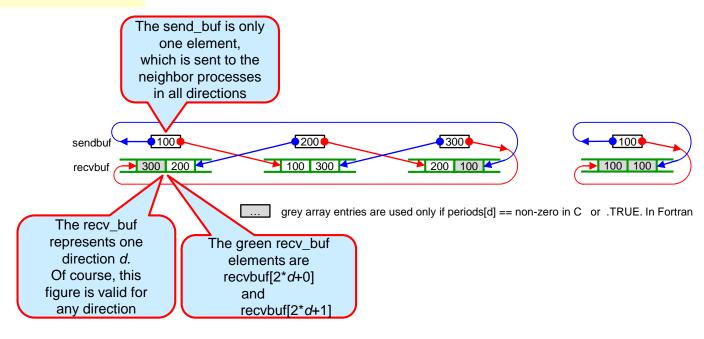

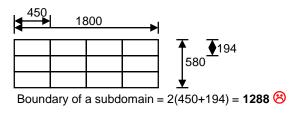

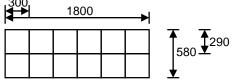

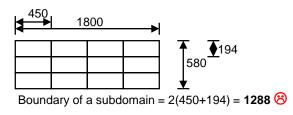

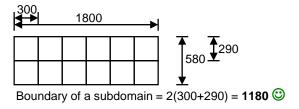

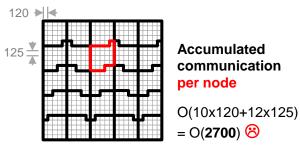

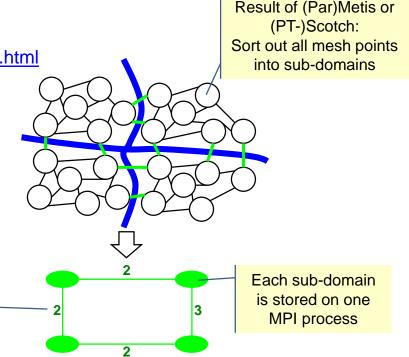

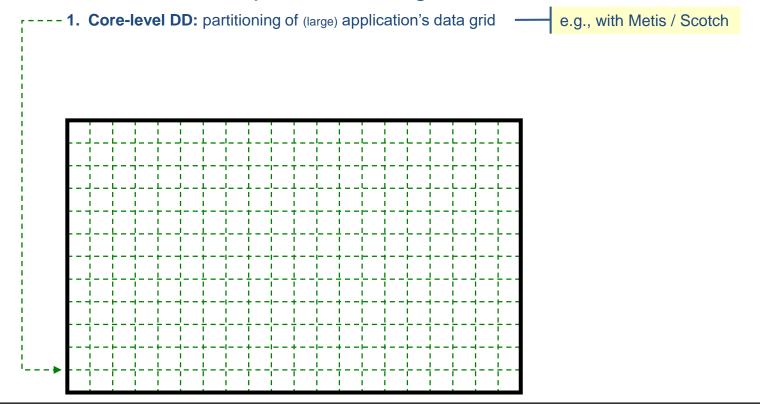

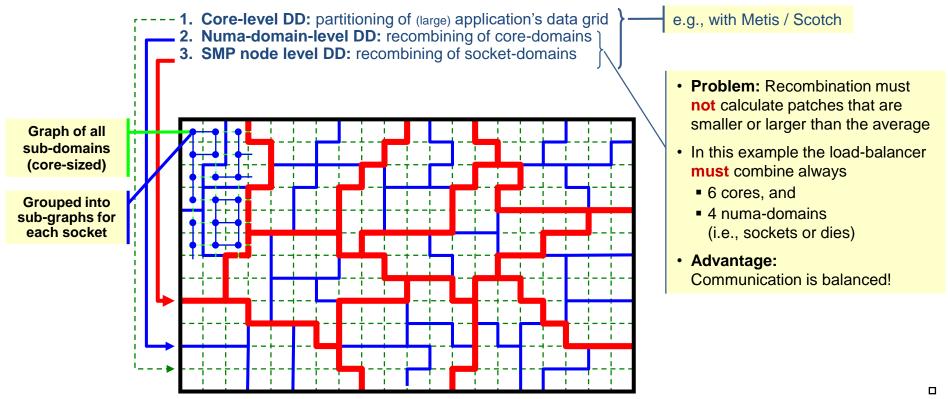

a[i] = b[i] + b[i-1] + b[i+1] + b[i-2]...;